Overview:

SPISim’s IBIS-AMI flow includes two main analysis features (also available as web-apps) for the design and verification of serializer/deserializer (SERDES) and DDR5 systems. These two features assist AMI modeling from two different perspectives:

- Top down flow: StatEye in Channel Sim Suite (or SPISim_Link web app):

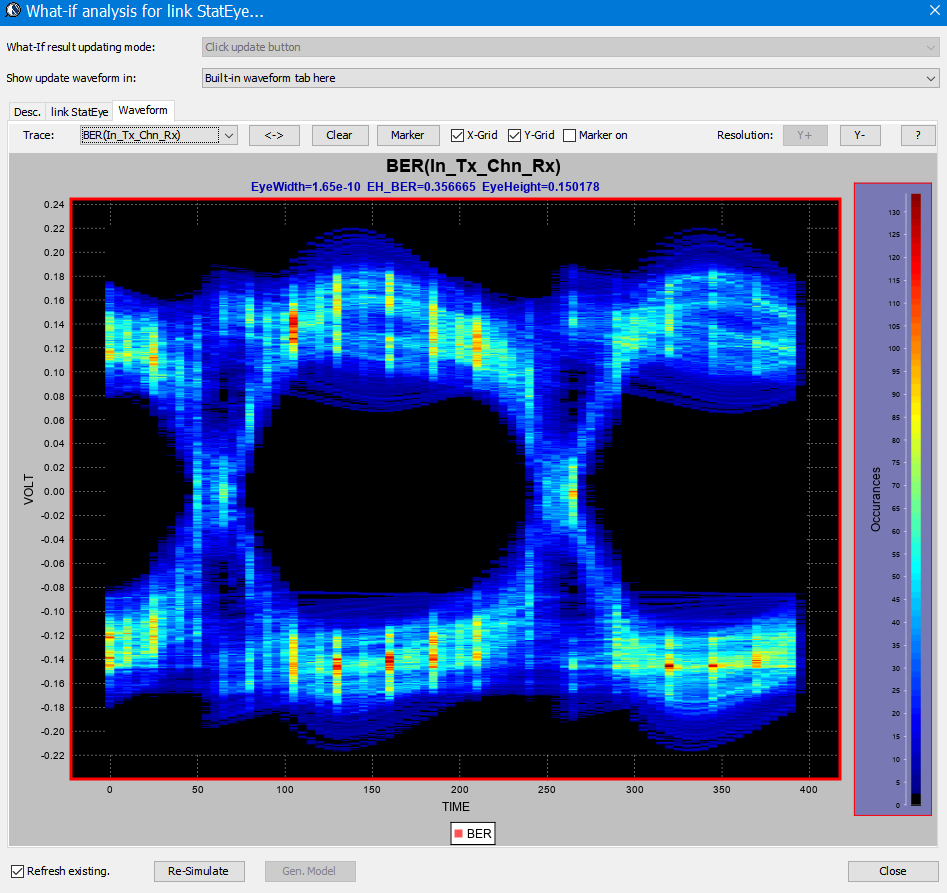

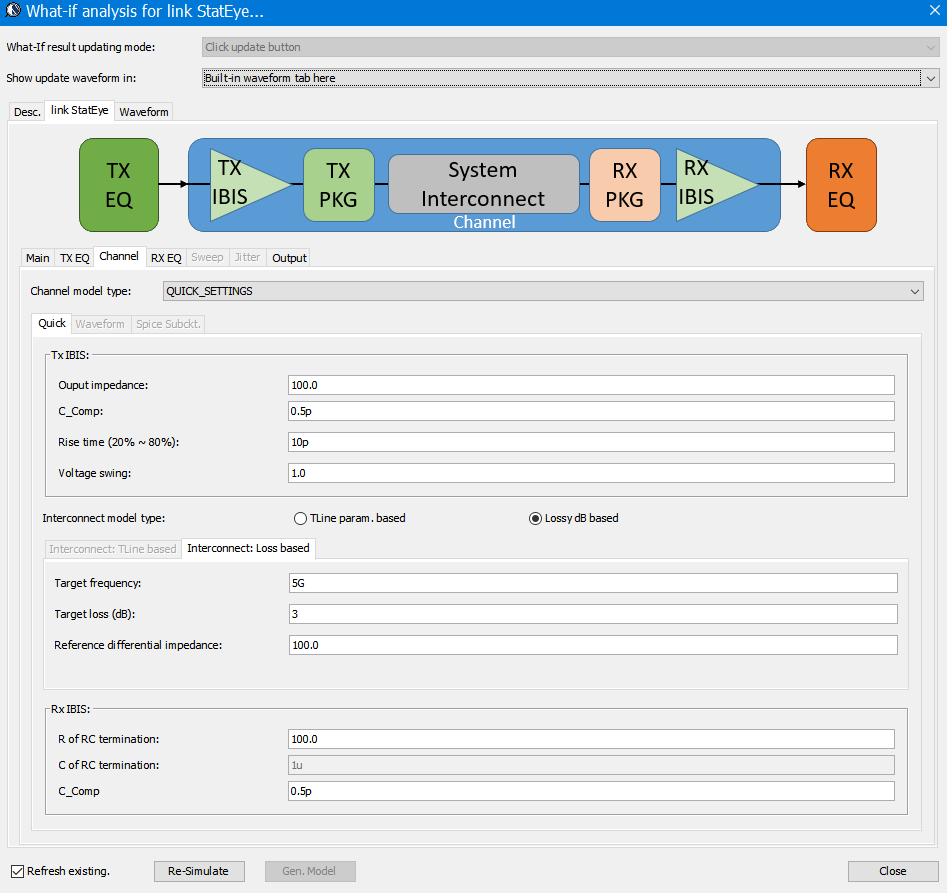

With this features, user can specify channels properties without any actual models at hand. This channel model will have analog-front-end effects usually caused by Tx or Rx IBIS and their C_Comps. For the EQ portion, AMI models from 3rd party vendor may be used. Alternatively, either Tx, Rx or both EQ models can also be generated in place via quick settings or “Spec. modeling” mentioned in next section. User then specify simulation properties such us signaling speed and simulation method etc to explore the overall performance via metrics such as eye diagram or BER plot. User can also explore different settings of AMI models involved for quick what-if analysis.

- Bottom up flow: Spec. AMI Gen in Modeling Suite (or SPISim_AMI web app):

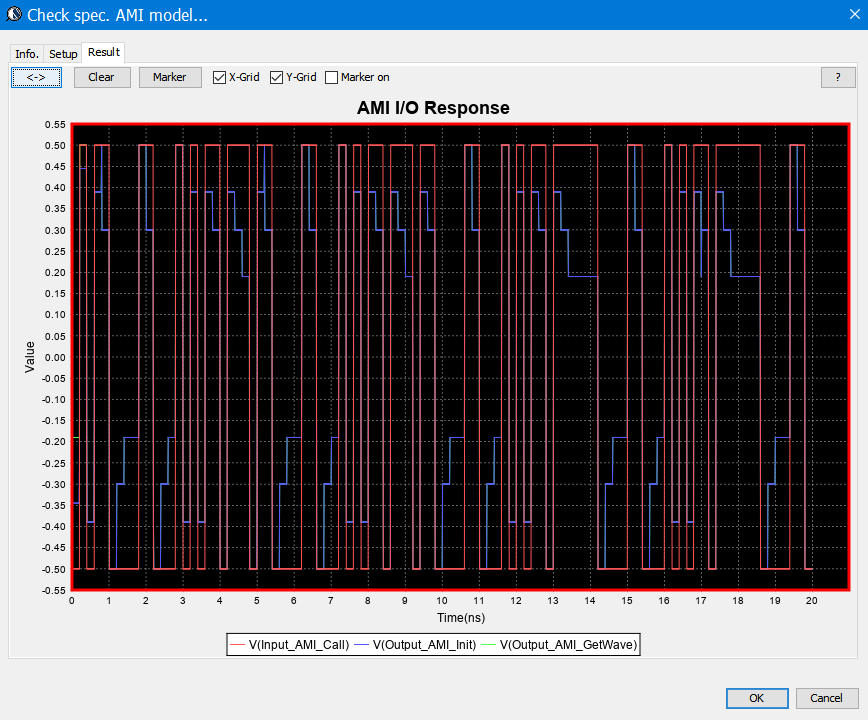

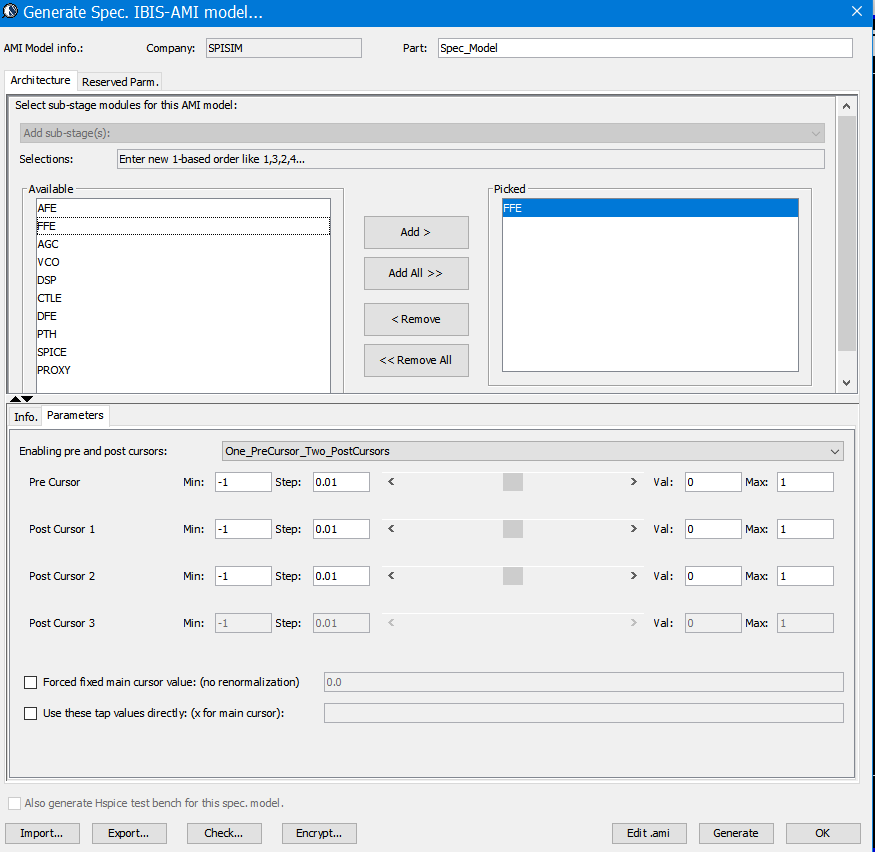

WIth building blocks such as FFE, CTLE, DFE, CDR, AGC and PassThrough (with VGA or soft clipping capabilities) etc, user can configure a particular AMI model then test drive with built-in stimulus or user provided waveform and see output performance. One or more such blocks can be cascaded to form stages for desired Tx or Rx capabilities.

In either case, user will be able to generate configured IBIS-AMI models in Win64, Win32 and Linux64 formats. These models have been pre-validated with commonly used 3rd party EDA vendors’ simulators so compatibility are assured. More over, the whole process does not require any C/C++ coding or compilation. The configuration settings are generated in the .ami file or can be assembled into a look-up table with user defined parameter names. This way model’s recipients will see exactly the same parameters used in the data sheets. The tabled data will be encrypted so the IP is properly protected.

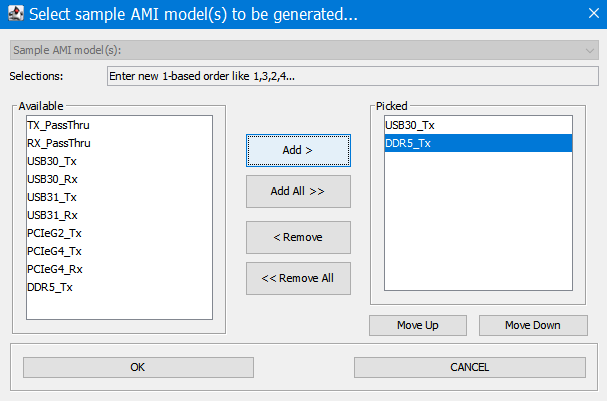

SPISim’s modeling suite with AMI also comes with several industrial standard IBIS-AMI models, they have been pre-configured and can be generated instantly. Further tuning is possible via either of the aforementioned flow to meet design requirements.

The following section discuss these flows and modules involved in more details:

- SERDES fundamentals and IBIS-AMI model’s roles

- Design and simulate SERDES systems with AMI

- Customize and export IBIS-AMI models

- Sample industry standard IBIS-AMI models