Before we are going to dive into details about buffer model, we need talk about why we care…

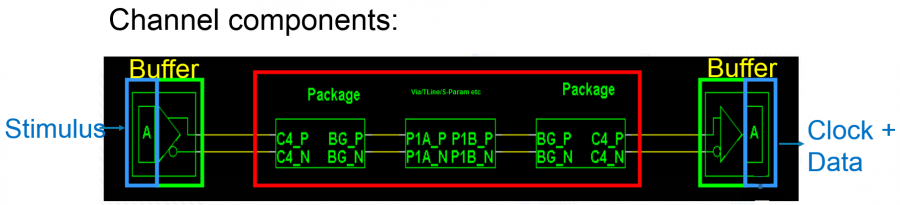

Buffers sit at the driving and receiving ends of a channel. So while the passive channel is composed of models like transmission lines, vias and connectors, the models sit at both ends are buffer.

If you are a circuit designer, in particular, a chipset designer, you pay attentions to the transistor sizing and the associated process, voltage and temperature corners (so called PVT corners) so that you will be assure that the designed buffer, when connected to the system, will have desired strength, impedance and timing.

However, if you are a system designer, or a signal integrity engineer. You pay attentions to higher level of the system design, such as component placement, routing, topology, termination etc. A buffer or an IC to you is just a component off the shelf. Those design details like transistor sizing, silicon doping concentration etc are too much details for you and are mostly not needed to what you are doing. Just like when software designer make connections between libraries, they make use of application interface (API). A much simplified model to represent these buffers are thus needed to enable system design.

Thus from the perspective of needs to interface between transistor level and system level design, a behavioral model representing a buffer is certainly needed.

Now when we talk about buffer modeling, there are several requirements derived from different perspectives:

A good buffer model needs to be:

- Accurate: This is most important consideration. Garbage in, garbage out. By accurate, it’s usually considered to be within 5% tolerance of corresponding original, transistor design.

- Protect IP: From IC/Chip set manufacturer’s perspective, they release buffer model mostly publicly to enable their customers adopt the design. However, they also do not want to reveal any IP such as how the buffer is designed and the manufacturing process info.

- Run very fast: From system designer’s view, a buffer needs to run very fast, typically at 100X ~ 1000X of the corresponding transistor design. Only so then system design, which usually includes hundreds’ or even thousands’ of buffer, is made possible.

- Easy to generate: For a model generation engineer’s perspective, if it takes lots of effort to generate and correlate the buffer model from its transistor counterparts, then the model generation process will become error prone and cause accuracy concern. Black-box type modeling is desired mostly as the model generation engineer does not need to know how these buffers are designed yet he/she can still generate buffer model which matches its original transistor’s performance.

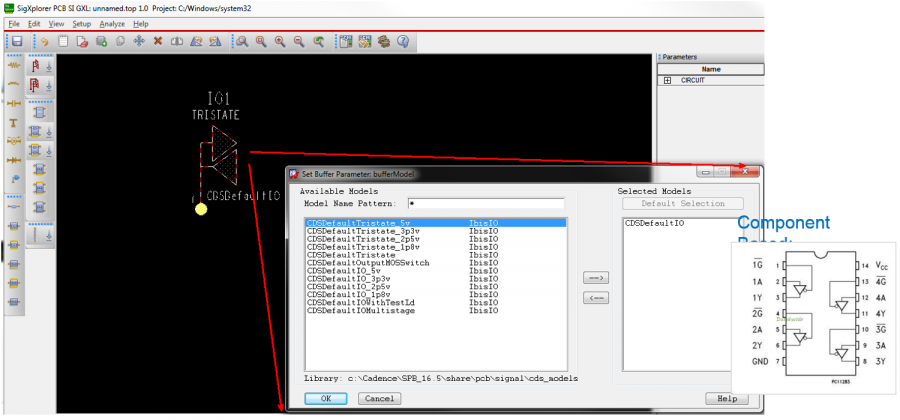

- Follow industry standard: A good buffer model should follow industrial spec. or format such that it can be simulated with different vendor’s tool, such as Synopsis’s Hspice, Cadence’s SystemSI or Agilent’s ADS. A model locked in to a particular tool is usually just to hide potential accuracy and easy generation issues down the road.Often in such considerations, one may consider using encrypted transistor netlist, such as encrypted Hspice, for model release. However, this will defeat the requirement of speedy simulation performance as encrypted model is usually run at the same speed of their transistor originals.From these considerations, several industrial standard have been proposed and widely used for buffer modeling used in system level analysis. They includes: IBIS and Verilog-A. In which, IBIS is most widely used and has been around since mid 1990. More info. about IBIS spec can be obtained from the ANSI’s IBIS website [HERE].