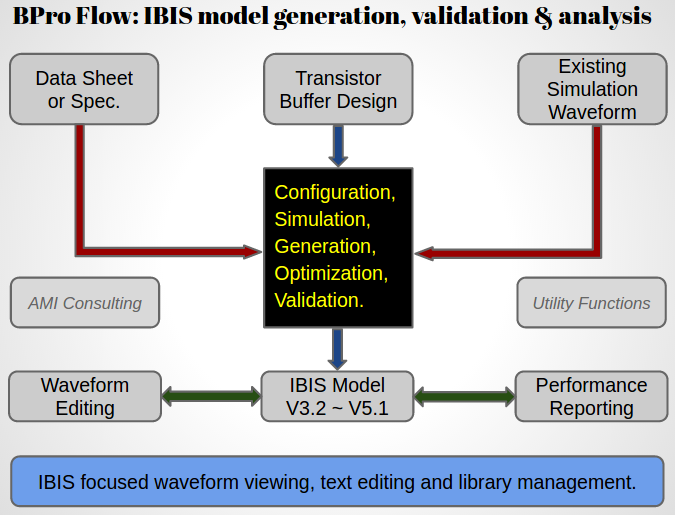

SPISim’s BPro Overview:

Design concept:

IO buffer modeling, mostly in IBIS spec. or Verilog-A, VHDL-AMS, is a crucial portion of the signal integrity analysis. SPIBPro (BPro for short) is designed to enable quick and accurate IBIS model generation and validation for system analysis. It implements industry’s best know methods in modeling methodologies and flow, and delivered in a easy to use, straightforward GUI presentation.

Environment:

BPro is an add-on of SPIMPro, SPISim’s modeling suite, on top of SPISim’s framework. This means BPro’s cross platform, all in one environment, and can use all the benefit MPro can provide, such as various plotting, optimization and even Verilog-A model generation.

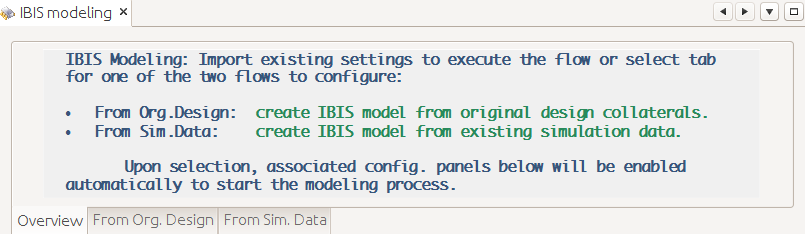

IBIS Modeling flow:

Here is the BPro’s IBIS modeling flow:

IBIS model generations:

BPro supports IBIS model generation from three different sources:

- From design spec. or data sheet: IBIS model together with two sets of waveform tables will be generated from spec. settings entered by user.

- From original buffer transistor design: If user has buffer design in spice format, associated technology file and control settings, he/she may generate IBIS model from scratch, with all intermediates data transparent to model creators for inspection or further tuning.

- From existing simulation data: IBIS model can also be created from existing simulation data. Generated models can be tuned to meet the performance, even though original spice netslit design is not available.

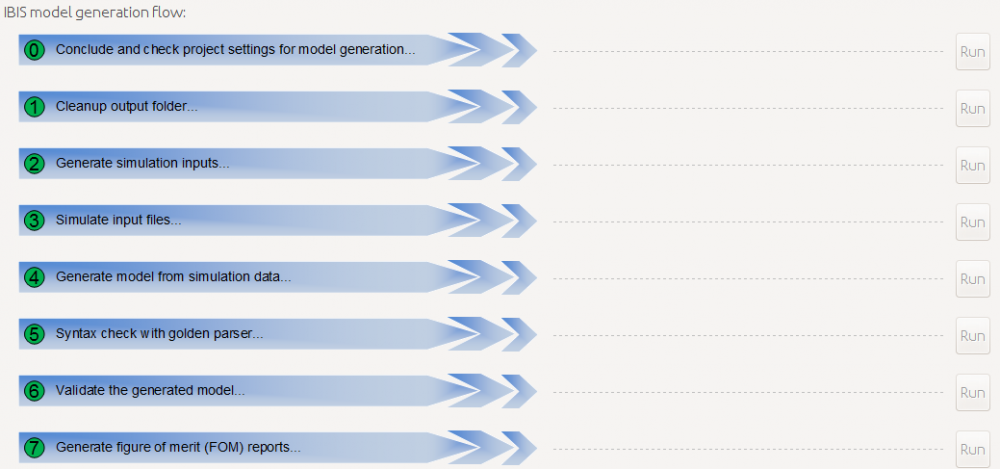

Generation flow:

Flow of modeling from spice design includes the following phases. Modeling from simulation data will skip step 2 and 3. An easy to follow, step-by-step GUI will guide user to walk through the process and complete model generation.

- Enter project settings;

- Generate simulation inputs;

- Simulate input files;

- Generate models from simulation data;

- Syntax check with golden parser;

- Validate generated IBIS model against original data;

- Performance parameters extraction and report.

All the data generated during this process, including spice file, simulation output in tr0/ac0 etc, generated ibs file and performance report in csv can be viewed/plotted in the same tool environment.

Model inspector:

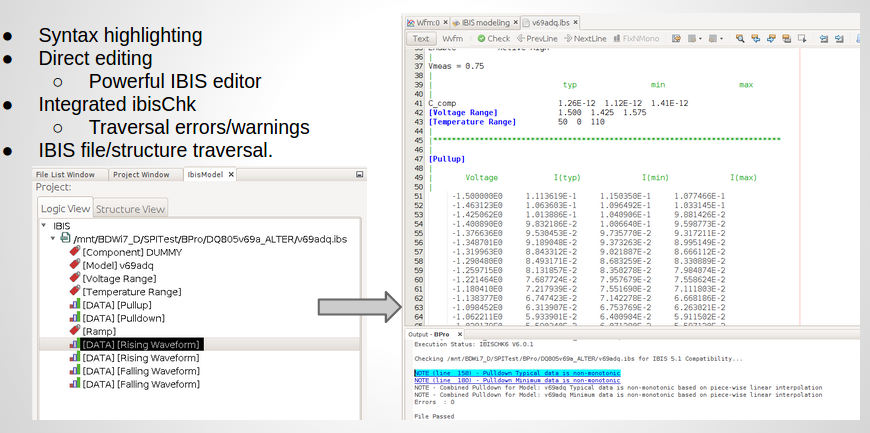

In addition to modeling flow, BPro also provides a model inspector to enable the following benefits:

- IBIS model library management and file data traversal;

- IBIS model data inspection in both texture and visual (waveform) style;

- Integration with golden parser to support syntax check in place and navigation of lines where errors or warnings occurs;

- IBIS syntax highlighted text editor and powerful waveform editor. Waveform editor enables user to manipulate existing waveform data, including change value, shift time, add extra or delete points. Final data will be re-synchronized across different Typ/Min/Max corners and populate into original ibis model.

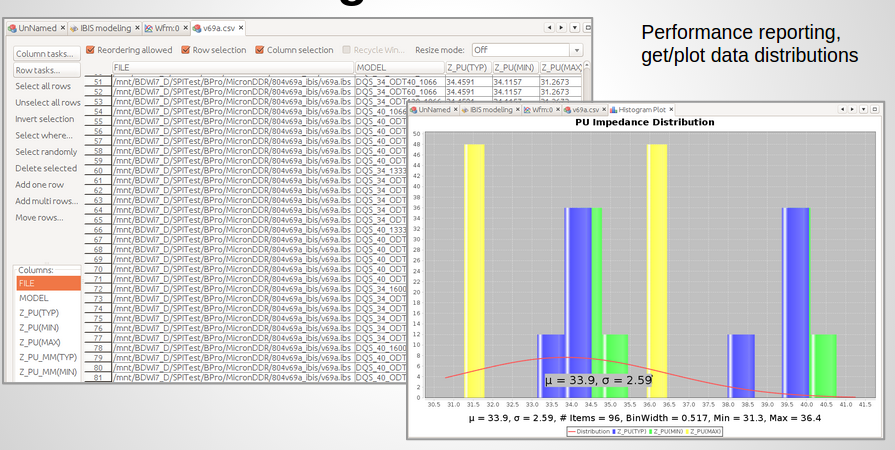

Performance report:

Performance of generated IBIS models or existing models in the library can be measured and report as a csv format. Multiple performance parameters may be selected for reporting. The result file can be plotted in many different styles for filtering purpose. This enable designer to filter and select models which meet their design requirement very easily.

Utility functions:

BPro also has several utility functions such as merging models into one IBIS file and more. Together, BPro provides a convenient yet powerful capabilities to meet system designers’ or signal integrity engineers’ needs.

Blog articles: You may also see a list of our blogged articles on this topic [HERE]