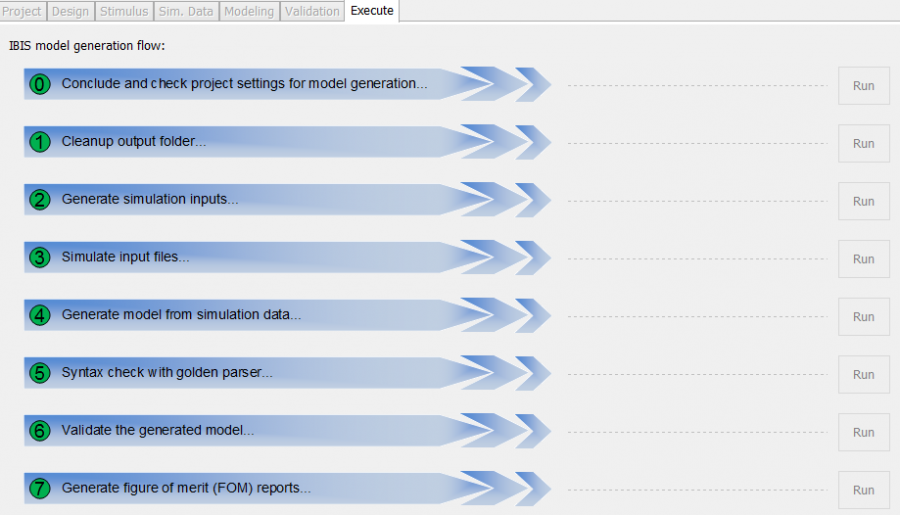

在前面的文章裡,我們簡述了IBIS模型內所需有的資料。這些資料多是以IV, VT, IT的波型表方式呈現;所以所謂的為IBIS建立模型,即是激發原來的緩沖器設計並進行仿真、最後再將仿真的結果進一步處理以合乎IBIS語法的模型表示出來。下面簡單列出了為IBIS建模所需進行的幾道程序:

- 搜集資料: 即獲得原緩沖器之設計資訊及相關操作係數;

- 產生電路: 為所用的仿真器產生模擬電路以適當激發緩沖器來運作;

- 進行仿真: 仿真上一步所產生的各種擬電路;

- 分析結果: 後罝處理仿真的結果, 並加以運算或轉換;

- 產生模型: 產生合乎IBIS語法的模型;

- 語法檢查: 用IBIS公用的程式(Golden Parser)來檢查產生的IBIS模型;

- 驗證模型: 為建立之IBIS模型產生相同操作情汜的電路並進行仿真;

- 產生報告: 替驗證的結果做出量化的報告,為模型加上如生廠商等的資訊等。

以下我們再對上列的步驟做進一步的說明:

- 搜集資料: 以下面圖中的緩沖器設計為例,欲為其建立模型,首先我們先要從設計工程師那裡取得詳細的設計檔案,其次, 我們也需要拿到這個設計生產時的製程係數:比如說是用那個製程(Process), 理想的供電電壓是多少(Voltage),以及預設的操作環境溫度等(Temperature), 這些參數一般統稱為(PVT係數)。最後,我們還需要知道這設計正常運作時端點該如何連接? 也就是說那個節點應該的偏壓是多少。當代的緩沖器設計常有許多控制腳位(Control Legs), 藉由不同腳位的通路與否,可決定了這個設計的諸如輸出電流強度及速度等的效能。以上資料缺一不可。都完備之後即可進行下一步:產生適當的電路以對激發緩沖器並為其進行仿真。

- 產生電路: 在這個步驟,我們需要產生各種電路以便能對其結果萃取出所需的IV/VT/IT資料波型。如之前所述:不同類型的緩沖器有不同的資料表需求,以下就為所需資料緩沖器需被激發運作的方式做一簡述:

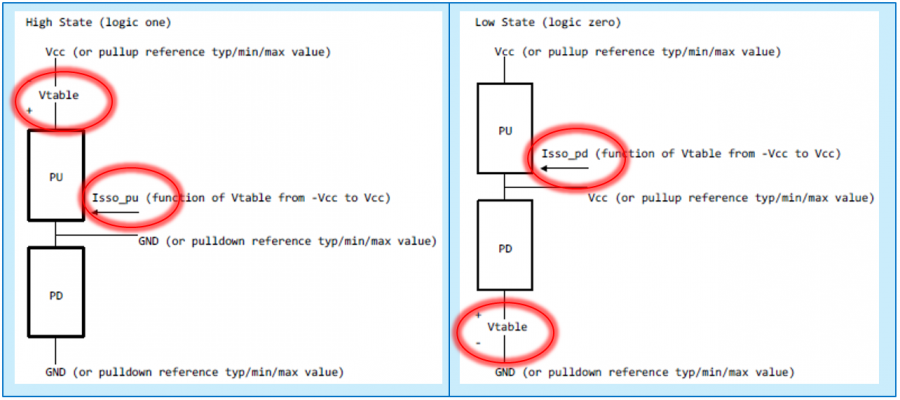

- IV for PU: 緩沖器需被致能(enable), 而後令其輸出邏輯1的高態,在輸出端以 -Vcc ~ 2Vcc進行掃描以獲得電流輸出/入資訊;

- IV for PD: 緩沖器需被致能(enable), 而後令其輸出邏輯0的低態,在輸出端以 -Vcc ~ 2Vcc進行掃描以獲得電流輸出/入資訊;

- IV for PC: 緩沖器需被放在高電阻態(High Z), 而後令其輸出邏輯1的高態,在輸出端以 -Vcc ~ 2Vcc進行掃描以獲得電流輸出/入資訊;

- IV for GC: 緩沖器需被放在高電阻態(High Z), 而後令其輸出邏輯0的低態,在輸出端以 -Vcc ~ 2Vcc進行掃描以獲得電流輸出/入資訊;

- ISSO PU: 在理想供電點及緩沖器上拉端口間接一電壓,電壓值自-Vcc~Vcc進行掃描,同時在輸出端量測輸出/入的電流資訊。這個設置模擬了緩沖器在非理想供電電壓的情況下,輸出電流的變化情形。(Voltage Droop)

- ISSO PD: 在理想接地點及緩沖器下端口間接一電壓,電壓值自-Vcc~Vcc進行掃描,同時在輸出端量測輸出/入的電流資訊。這個設置模擬了緩沖器在非理想接地的情況下,輸出電流的變化情形。(Ground Bounce)

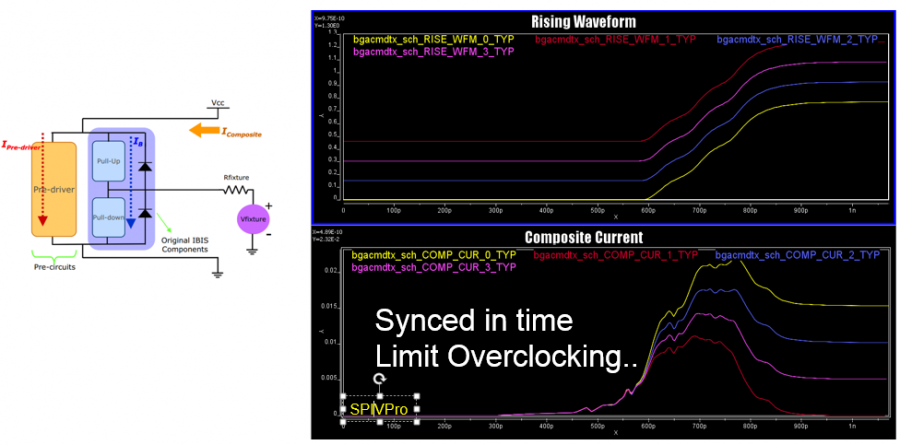

- VT for rising/falling waveform: 緩沖器的輸出端需連上測試電阻及電壓等的電路,以合乎實際情形(如100ps的上升時間)的數位信號輸入, 同時在輸出端量測瞬態的電壓波形。這種電路應對不同的測試負載情況再做一次。這兩組的測試情況應足以涵蓋了實際運作情況的操作範圍。

- IT for composite current: 在緩沖器的上拉端口接一零電壓差的電壓源、用以監測流過的電流。在如同VT電路的測試負載運作時,量測並記錄這電流值。基本上IT 和VT的電路分析可在同一次仿真中同時進行。

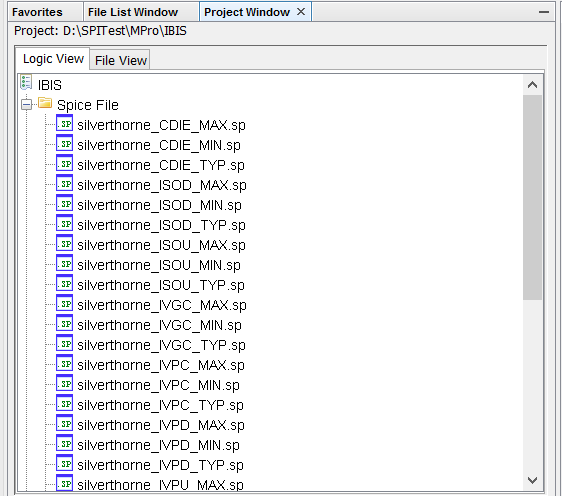

- 進行仿真: 以上所產生的電路可分別放在不同的檔案…每個檔案只針對一個不同的資料仿宜需求, 抑或是它們都放在同一個檔案裡, 再用如HSpice裡的.alter依序進行仿真。前者的好處是不同的檔案可在同一機器上的不同執行緒裡、或是不同機器上同時進行仿真以結省建模時間。有些緩沖器的設計需含有時脈(Clock)的輸入, 在這種情況下穩態的掃描(DC Sweep)則不可得, 而得透過如假瞬態分析的方式才能得到結果。這分析技巧也套用在一些不易在DC仿真收斂的設計。

- 分析結果: 這一步所要做的是對仿真結果讀出及計算。比如說要將無法剔除、一直都會有的PC/GC逆向偏壓時漏電電流自PU/PD電流裡減去, 以及將PU/PC的結果轉換為對VCC而非對地等等。 若是緩沖器還含有 on-die termination, 則PC/GC仿真所得的電流將不容忽略,而得進行更複雜的[如此所述]的運算。

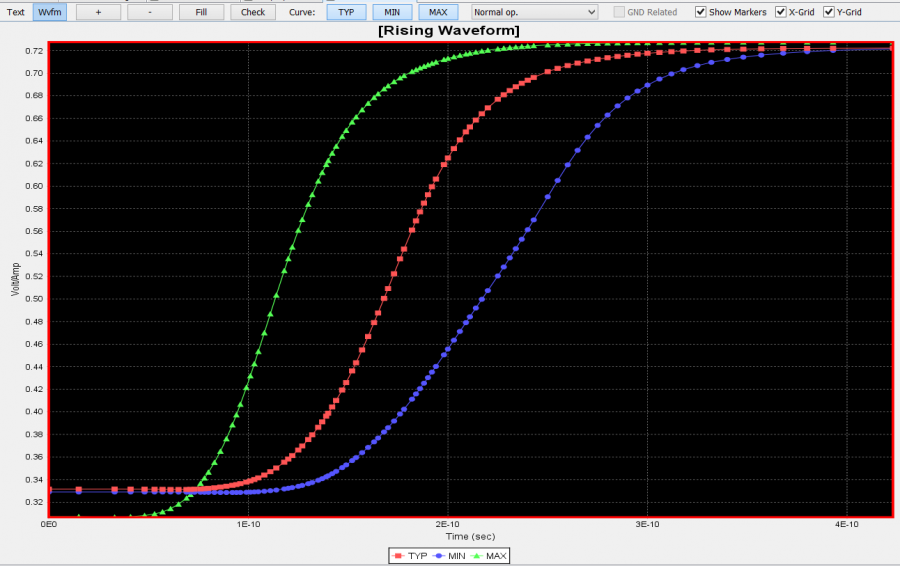

- 產生模型: 有了結果後,便是將其轉換成合乎IBIS模型的語法並輸出成檔案了。 為了使模型準確而精簡, 優化的程序常是不可或缺的。優化的需求在於仿真的時域結果常包含了上千甚至是上萬個資料點,但IBIS V3.2的規格只準許運用100個點。即便是IBIS V5.0 後準許用更多個點數,也因為Composite Current常是非常波動而不平緩的, 所以仍需要對現有資料點分析以選用最佳的點來表示波型。其次, 在IBIS的資料表裡TYP/MIN/MAX的各個欄位都有同樣的時間點(同一行表同一時間點), 這更曾加了優化的需求及難度。因為優化的程序需同時考量到三組波型資料的取捨。

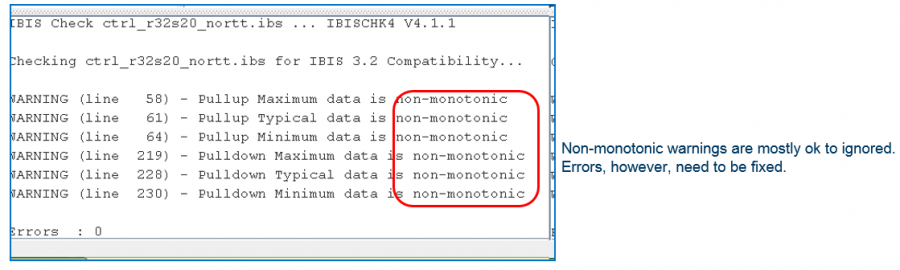

- 語法檢查: 有了IBIS模型後,便需以IBIS委員會公開發佈的語法檢查器(Golden Parser)來檢查。除了一般語法外,它也會偵測可能的穩態電壓誤差。當誤差值大過容許值時,警告便變成了錯誤…一般業界的仿真器是不會對含有錯誤的IBIS模型進行分析仿真的。所以根除錯誤及了解並儘量減少警告的標示便是極重要的工作。

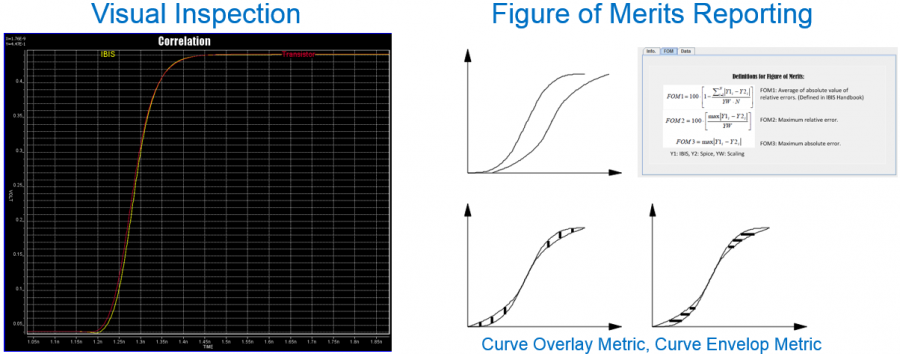

- 驗證模型: 有了合乎語法的模型,下一步是為其建立如原緩沖器相同的測試負載情況下的電路來進行仿真。一個好的IBIS模型應是準確、精簡、且運作迅速的。所以這些電路應跑得非常快。當有了結果後就可先以視覺上將模型及原設計在同一測試負載情況下的結果一同比較。一般信號輸入到輸出間的延遲是不能由IBIS模型的所重建出來的。所以如果除經果些許的時間位移外,兩者的上升及下降波形都很近似、而且穩態的(高/低)電壓也都相符,則這就是一個可接受的IBIS模型。

- 產生報告: 替驗證的結果做出量化的報告也常是建模標準之一, 以下的兩份資料已為量化的標準做了一些規範:IBIS accuracy handbook and quality spec. 對於圖形驗證上, 一種品質因數(Figure of merits)常被用來表示所建出模形和原設計在同一負載時輸出波形的相似度。

以上我們簡單敍述了欲為緩沖器建立IBIS模型所需經過的程序。所謂”魔鬼藏在細節裡”, 很多細節之處雖是值得深入探討、但已在本篇文章的範圍之外。實務上來說, 以人工手動的方式來建立IBIS模型雖是可以做得到、但往往是曠日費時又易生錯誤。這也就是為什麼我們SPISim 使必信科技研發BPro模組來簡化這項建模工作的原因。