我們將在此文談到如何對IBIS模型資料進行除錯及超頻調校;如之前文章所述,IBIS建模程序中首先的驗證程序即是以Golden Parser為模型進行檢查,若模型資料有問題,則一般會看到下列的錯誤訊息:

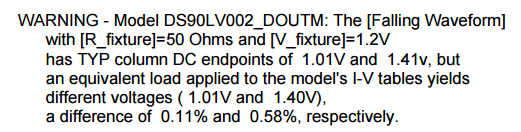

- DC mismatch: 即VT及IV穩態資料間相衝突;

- Non-monotonic data points in I/V curve;

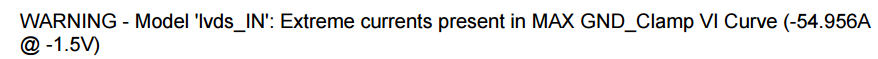

- Extreme currents in IV data。

我們將在以下為這些錯誤訊息詳做解釋。至於效能調校部份,我們將談談IBIS模型的超頻及其可能衍生的精確性顧慮;為確保您產生的模型可在預定的時脈速度下運作,確保其工作頻率的準確性是很重要的課題。最後,我們也將簡單談談我們使必信科技發展出來的工具裡是如何來克服這些技術上的挑戰。

DC mismatch:

IBIS建模程序中最麻煩的莫過於碰到下面的錯誤訊息:

當發生這種誤差(mismatch)時,建模者所會看到的是在VT的穩態部份電壓和自原緩沖器設計(Transistor)跑出來的結果位準不同。一般的解決方式是回頭去檢查穩態分析部份(IV:PU/PD/PC/GC)設定偏壓是否正確,而後重新仿真、產生模型後再測一次。最後不得已的手段則是手動地去改資料點,以便能減輕這種誤差的程度至可接受的範圍、或是讓其完全消失。不論何種方式,我們都得先對這個誤差的成因做一了解才不會如瞎子摸象不知從何修起。

VT 波型資料的起迄點均被視為已達穩態;也就是說,不論時間點(橫軸)的變化,這兩點的電壓均不再變化。Golden Parser即取這兩點的值來算出由VT所顯現出的負載電流。

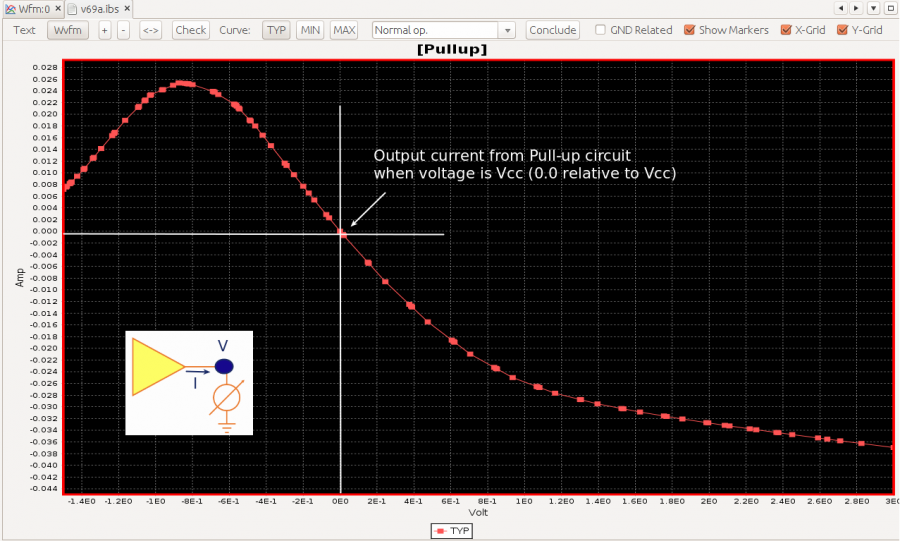

上圖中, 我們在左下方簡單表示了緩沖器的負載情形,輸出電流I取決於端點電壓及其輸出的負載,也就是說,當VT達到穩態時,吾人可由模型裡的負載組合來做下列的試算:

- I_LoadLine = (V_Pad – V_Fixture) / R_Fixture

其中Fixture部份即測試負載、而PAD即緩沖器的輸出端口。從電路來上來看,當緩沖器輸出為高態時,大部份的電流都是由上拉電路PU所貢獻;下拉電路PD此時可看作是完全地斷路而不提供任何電流的。若我們以V_Pad為值,減去Vcc(因為PU的X值是相對應於Vcc的, 即Vcc relative),則可用PU的IV資料表來找出相對應的輸出電流。然後,由於靜電保護電路PC/GC均在反向偏壓的狀態,我們也可用同樣的方式及值(PC也是Vcc relative)來找出相對應的電流。總結而言,由IV資訊所顯示出的應有的電流輸出即是I_Out=I_PU-I_PC-I_GC;所謂的DC Mismatch即表示這由IV所算出的輸出電流I_Out和由VT資料所算出的應有的負載電流I_LoadLine並不相同。

我們剛剛提到的只是輸出高態的部份,輸出為低態的情況也是一樣,只不過在低態時,上拉電路可視為完全斷路。故大部份的電流都是由下拉電路PD所提供。

由於一個IBIS模型裡可以有好幾組VT表,每個表產生時的測試負載均不相同,所以這個DC Mismatch的問題一旦產生,常是每個VT表的兩個靜態值都會有錯誤而顯得錯誤很多。

由上所述:mismatch的成因在於IV及VT所提供的資料對算出來的輸出電流不相符合,則修正之道即在於改變IV或VT以使再算出來的資料能相符。通當建模者需回頭檢視當初在做穩態仿真時偏壓是否正確,或是在“偽穩態分析”時輸入的電壓是否改變過快而使量得的電流並不真是像穩態時的值。一般來說,VT的瞬態仿真一般是較沒問題的。因為若VT有問題的話,在其仿真結果上就可很直接的發現出錯誤。

Non-Monotonic Points in I/V data:

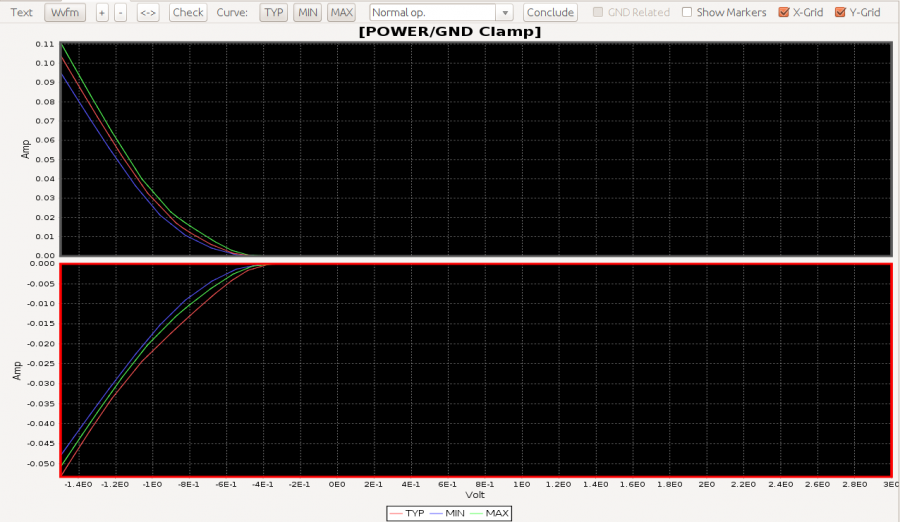

這訊息意謂資料表裡的值為非單調性增加或減少;也就是其一階導數有正負性變化的問題。一般而言這類的警示是可被忽略的。唯有在非單調性增加/減少情況較嚴重時,仿真器會在這部份的範圍有不收歛的可能,因其一階導數(找牛頓解用)之不穩定變化之故。

這些資料表裡的問題點常是在緩沖器的非工作區間,故解決之道之一是也可以用人工的方式去消去一些點或增加一些點使得其看起來更平滑些。要注意的是有些緩沖器的設計在先天上就會有這些非單調性存在。故若使用模型的人對這類的緩沖器有所了解,則事後人為的改變資料反而會使的建出來的模型看起來像是假造的而有精確上的顧慮。

這類的警示或錯誤訊息常發生在代表靜電保護電路(ESD)的PC/GC資料上。另一種情況是上拉下拉電路的穩態仿真結果不對。因為PC/GC的逆向雷流無所不在,故在建模過程中,當將由PC/GC的電流自PU/PD電流做減去的運算是便使得PU/PD也顯示出了如PC/GC般的崩潰區曲線而形成大電流的通過。

如上所示,一般在正常工作區間,PC/GC兩者都是反向偏壓的。。。在很大的範圍內都是平線且值很小(即漏電電流很小);唯有在崩潰區才有如指數般的電流成長。惟由於IBIS規格中,為將遠端之全反射列入考慮而有的-Vcc ~ 2Vcc掃描區間的要求,故ESD電路便可能在這些很少可能才發生的時候顯出高電流。解決之道一般是在開始進入崩潰區的一伏特後對在那之後的電壓做線性外插。如此一來電流在模型裡將不再是指數性、而是變線性的改變。於此同時當ESD發生作用時也會有足夠的崩潰電流在仿真時保護連接到緩沖器輸出端的電路。

超頻(Overclocking):

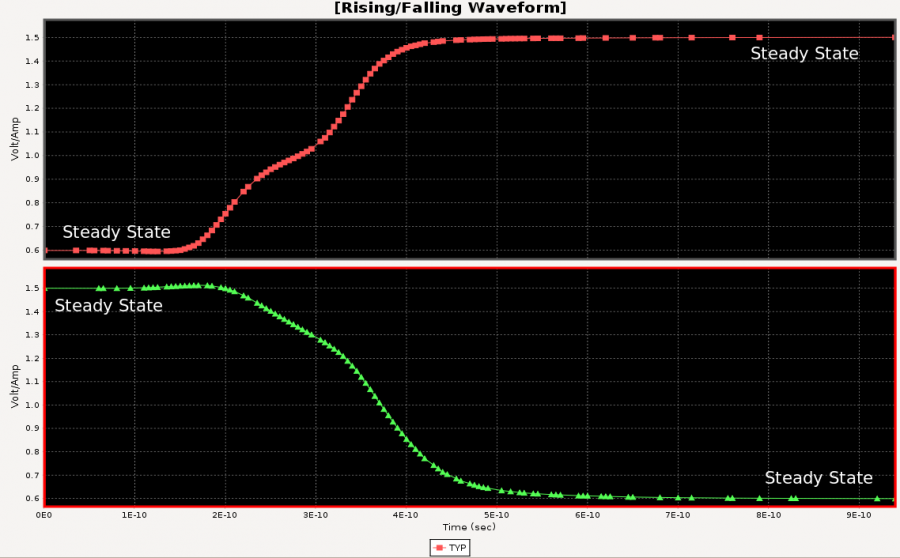

每一組瞬態的上升/下降時態曲線加起來可表示出此一緩沖器模型運作的最小週期T。而這模型可運作的最高頻率即為此週期的倒數FMax = 1 / T; 也就是說:週期愈短,模型在不被仿真器更改資料的前題下可運作的工作頻率也就愈高。

若在真實運作時(如在通信渠道裡全仿真時),若操作頻率超過了如前所述的FMax, 這個模型便是在被超頻。一個被超頻運作的模型將有精確性及效能一致性上的顅慮產生。

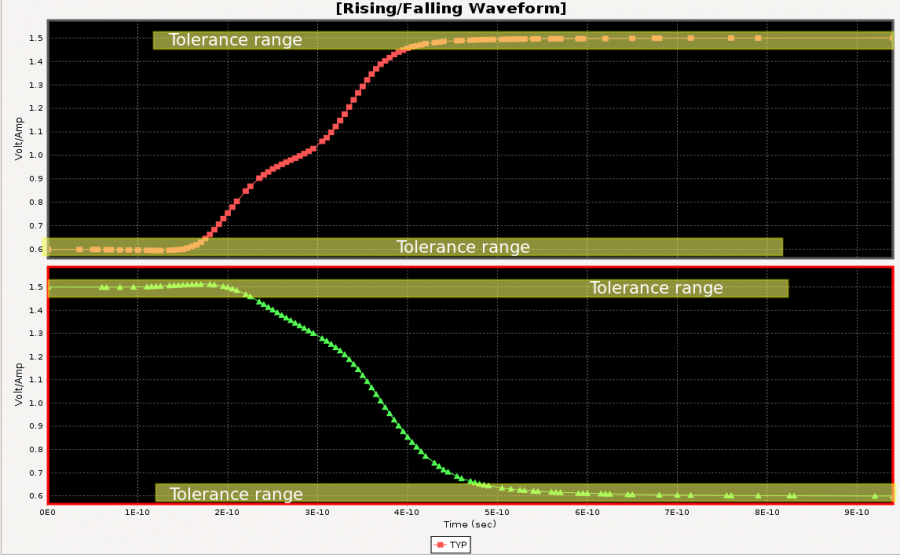

上圖中,有很長的一段時間緩沖器的輸出都是在穩態的情況下。若建模時能將這些部分、外加上一些容許範圍、地被移走;則最後留下的VT部份將維時甚短, 這表示雖然大部份的上升/下降時的變化情形仍在建出模型中,但這個新模型將可以更快的頻率來運作。

上圖中,有很長的一段時間緩沖器的輸出都是在穩態的情況下。若建模時能將這些部分、外加上一些容許範圍、地被移走;則最後留下的VT部份將維時甚短, 這表示雖然大部份的上升/下降時的變化情形仍在建出模型中,但這個新模型將可以更快的頻率來運作。

一般而言,業界裡常用的仿真器都可透過參數來進行如此的調校。問題在於在IBIS規格裡並未對一仿真器應如何消去這些穩態資訊來定義。其結果便是兩家仿真器對同一模型在超頻時所產生的結果可能不同。作為一個建模工程師,您不應對將有可能使用您產生模型的用戶為他們做仿真器使用上的限制。所以較理想之道應是您在建模之初便能將這些穩態資料點適做處理,並在模型表頭的部分明列這模形可操作的最高工作頻率。

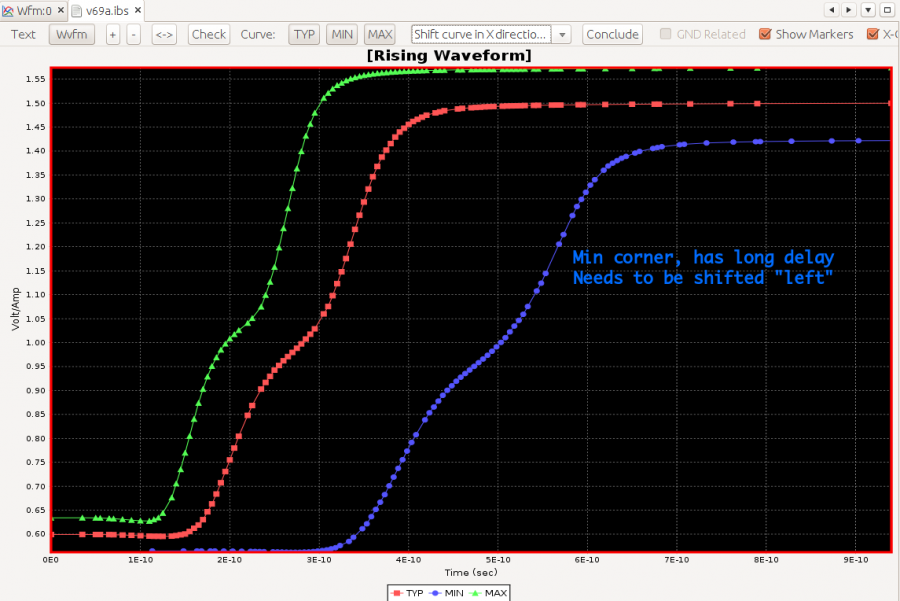

上面的圖表則列出了另一種可能形成超頻的原因。圖中MIN曲線的延遲遠比其它兩者(TYP/MAX)來得多。由於IBIS規格裡要求三者在模型裡均由同一橫行、即時間點、來表示;上面的圖形將可能形成超長的MIN曲線的起始穩態值而很可能地自動變超頻。有些時候甚至還沒法及時將MIN曲線的資料完全含括在欲建的IBIS模型中。

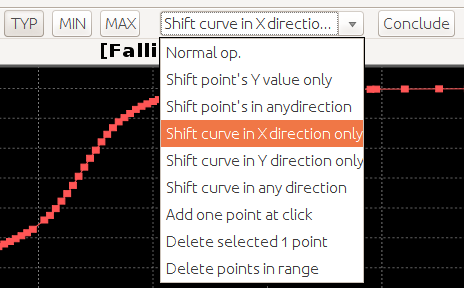

為了解決這些技術上的問題,我們使必信科技BPro模組裡的解決方式是該建模者有更大多的操作選項可以來移除這些穩態資料。移除之後再由我們的工具自動地計算並優化以避免造成之前所述的DC Mismatch的問題。最後,我們也在同一模組中提供了直覺的工具供建模者可以手動地為現在模型資料做調整。

最後要再加以註解的是:以上所述僅限於電壓部份的資料除錯及調校。對於IBIS 5.0後的模型、因其亦含有輸入電流的資訊、故要考慮的面向也就更多了。舉例而言:這些輸入的電流因也含有前級部份切換電路的部份,故很有可能在緩沖器輸出的電壓還仍在穩態時(還沒開始上升或下降)就有很大的波動性。因為VT和Composite Current 的IT在時間上是連動的,故吾人就不能隨意地將一開始時的穩態資料做移除,因為這麼一來輸入電流部份的時間點就不對了。凡此種種,將再在日後的文章中另作討論。