元件在仿真器內運作的順序大致上是:先將網表上所給的原始設定轉為仿真過程中內部所需的資料結構(Parse)、在DC未開始之前將物理模形轉成(Model)諾頓等效電路之形式,而後在每一時步或每一時步的牛頓迴圈中更新(Solve)等效電路參數值並將其填入(Stamp)系統矩陣中,最後在每時步或仿真結束前將其資料傳給上層以便記錄後處理或直接寫成波形檔(Query)。這其間的“Model”與”Solve”的設計便是仿真器設計中需對元件物理要有的理解才能順利完成的。

在這兩篇貼文中,我們將大致談談系統元件中IBIS、傳輸線及S-參數等是怎麼被建模(Model)及求解(Solve)的。

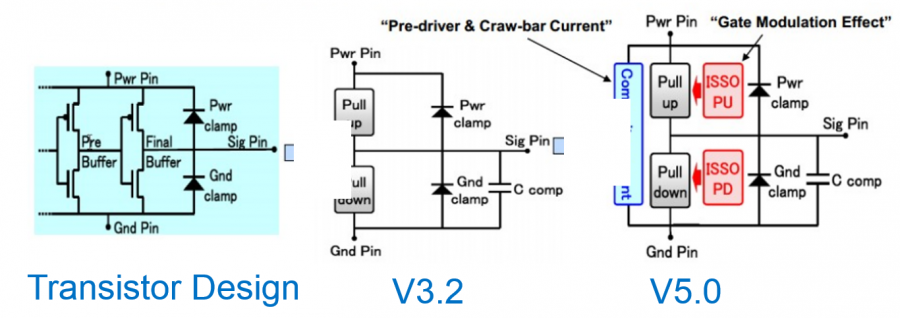

B-Element… IBIS:

我們之前已對IBIS寫過幾篇貼文,同時也由下面的IBIS結構中便可對如何建模猜得一二:

這幾組IV曲線: pull-up, pull-down, power clamp and ground clamp基本上就是非線性電阻,亦即其電阻值隨著兩端點的瞬態電壓而改變;故在牛頓迴圈裡,程式只要利用其電壓差來在之前Parse得的曲線做線性內插即可。實務上因為這種內插要進行很多次。。若每次都從第一點開始掃描點落在的區間則效率不佳,故可先建成線性方程以增進查值速度。

上述IV曲線之外,瞬態波形轉出的切換係數switching coefficient及合成電流composite current 兩者都是與時間點有關的,其作用可視為是一個乘數來對靜態算出的電流再加以限制。切換係數的目的是要確認IBIS在連到表定的負載時,在端點會有如waveform table一樣的響應。而這係數是在仿真過程中只要事先計算一次即可的,故可在Model步驟中完成。最後至於C_Comp,若可能的話可直接加入仿真器已有的電容器串列中而不需要自行管理有關error prediction及積分等的事宜。

大致上來說,為IBIS元件編程較複雜之處多是因為不同的模型參數可能有不同的skew,而其間可能的不同組合(比如說fast 和slow就會由不同參數中typ, min, max組合而成)便得對簿計先事先規劃;其次,因為在同一元件裡,除主IBIS外也可能會有submodel, driver schedule等的附加IBIS模型以達成pre-emphasis等的等化功能,故在軟體的設計上可能也得考慮如composite pattern以便能以一模版來遞迴地加入主要及附加IBIS模形部份。最終而言,IBIS元件的建模是相對容易的。。尤其是如果跟即將要提的傳輸線相比的話。

W-Element… 傳輸線:

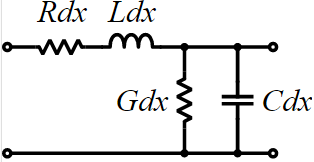

每本電磁學教科數裡都會列出如下傳輸線單位長度dx上的RLGC基本模型:

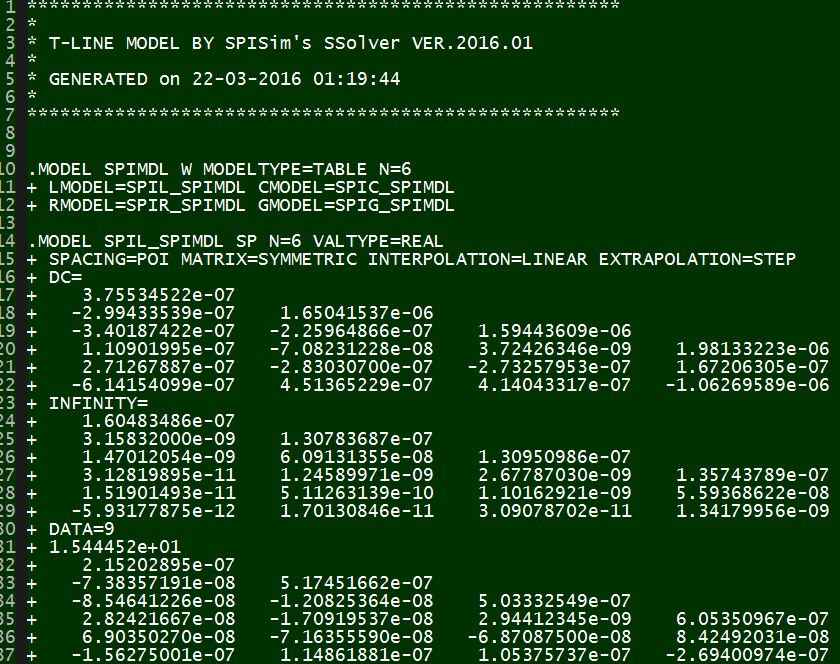

在含HSpice的許多仿真器裡,上述的模型多以U-element建成,即(Uniform distributed model);由於使用者得事先決定要以多少單位長度(dx)來建模,再加上仿真效率上的考量,這種U元件多已不被使用了。話雖如此,傳輸線的基本模型資料(frequency dependent tabular model, or tab model)仍是以這種形式儲存的:

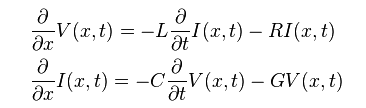

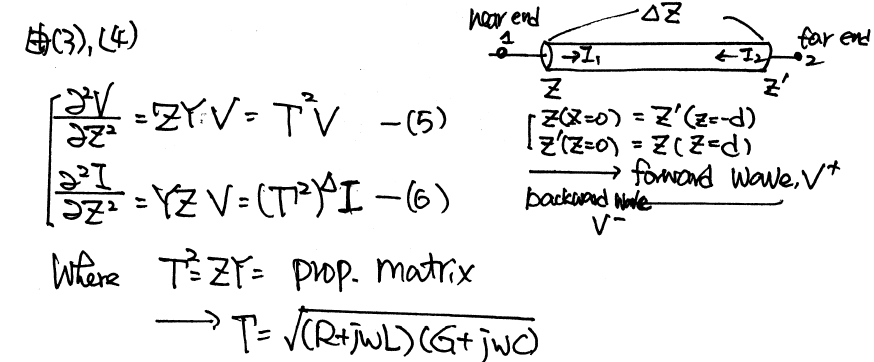

這種tab model一般是由二維場解器依PCB疊層、走線寬度、疊層間界質之物理特性(如導電度,介電常數等等)甚至是粗糙度後處理(surface roughness treatment)等照Maxwell的邊界值條件在不同頻率上解出而來;一般上也都必需要有低頻(近DC)、高頻(50G或100G)及其間不同的頻率點的值才算完整。那要如何將這原始資料轉成可仿真的線性模型呢?一般可從電報者等式 Telegrapher’s equations 開始著手:藉由解出單位長度下RLGC的KCL/KVL,我們可得到一階導數式:

而這兩列微分方程的解,即如上述wiki連結裡所示,為一含有傳播函數Gamma T的波方程 :

當把這系統模型之解寫成有如線性式時,便有如下的諾頓等效電路:

在傳輸線近端及遠端的電路裡,都有兩個部份:其一是在瞬態當下的電抗Z(s),其二是由彼端入射或反射、經傳播遲延而傳來的電流源。這兩者在上圖都仍是頻域值,故在時域仿真時,均需再進一步地轉化成可積分的形式才能在不同時步中stamp入矩陣。綜上而言,傳輸線元件的仿真步驟為:

- 讀取並儲存原始的tabular model;

- 利用上者最高頻率值(或利用外插)來算出此線之傳播遲延及特性阻抗,這兩值將使用在後面的時域仿真中;

- 在頻域中建模出上面系統模形裡的阻抗響應Z(s)及傳播響應r(s),因傳輸線可能是有多條線藕合在一起的,故這些響應式多是多維的矩陣;

- 利用Vector fitting 的技巧以數個極零點來模擬上述Z(s)及r(s)的曲線,在大多數的情形下(尤其是當原始模型資料不足或ill-behaved時)要很完美的能去map這些曲線可說是不太可能的,則需採minimum-square-error等的方式如來求近似曲線的極零值;

- 一旦有極零點,便可將每個term都轉成相對應的時域函數,而這所有的term在時域上的組成即是其在時域上的響應。例如Pade’s approximation就是同樣的原理;

- 在時域仿真時,每一時步中都對彼端在傳播遲延時間前的歷使值利用內插的方式來得現值r(t),這現值再和當下的Z(t)一起組成等效電路填值於矩陣中;

- 在頻域仿真則簡單得多:可跳過vector fitting及轉成時域積分式的步驟而可直接內插出當下頻率的Z(s), r(s)來使用。

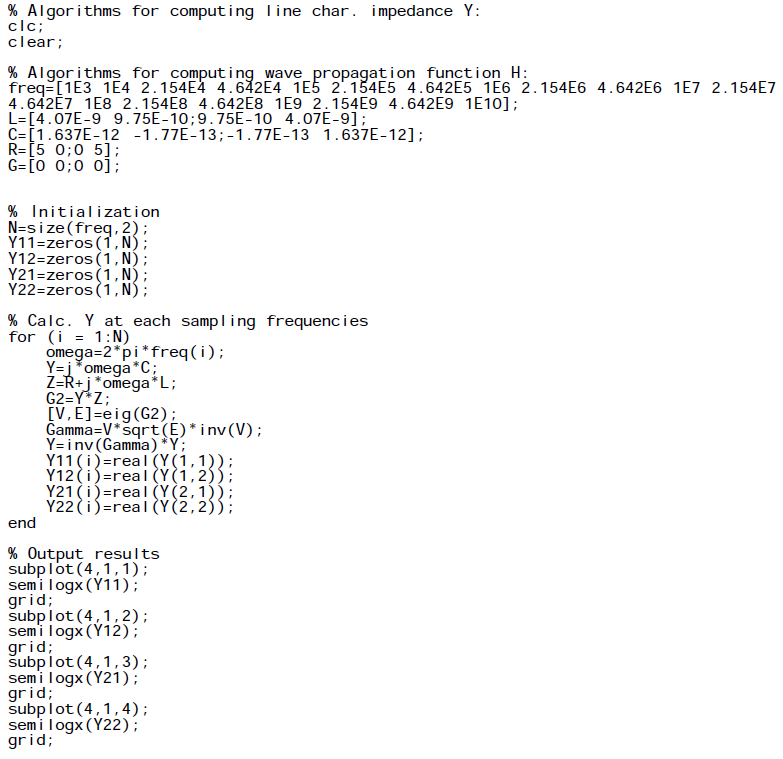

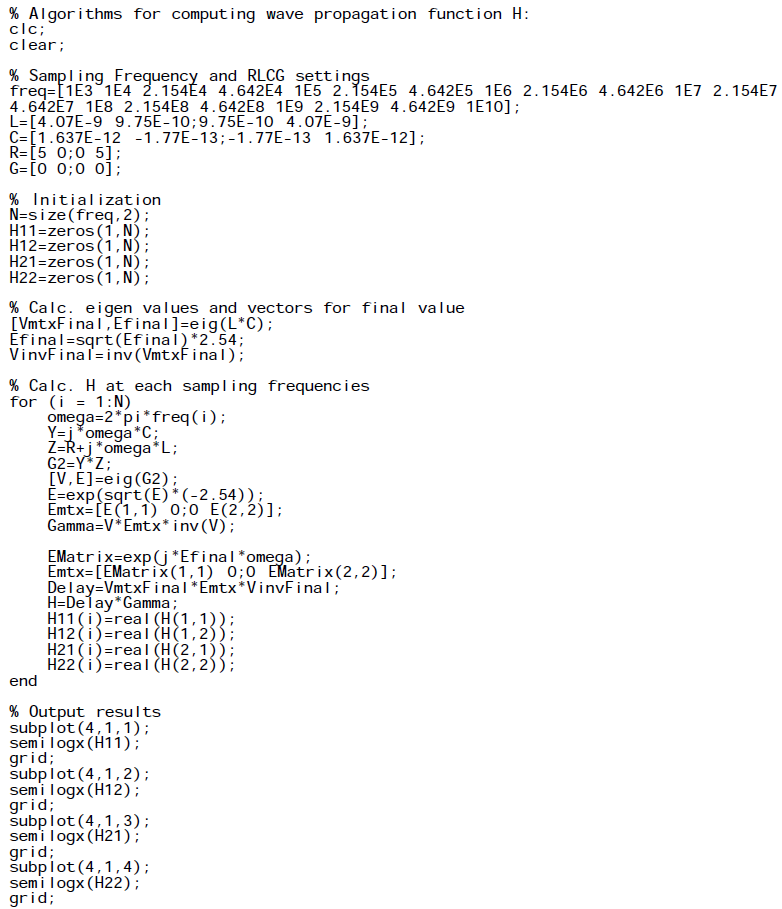

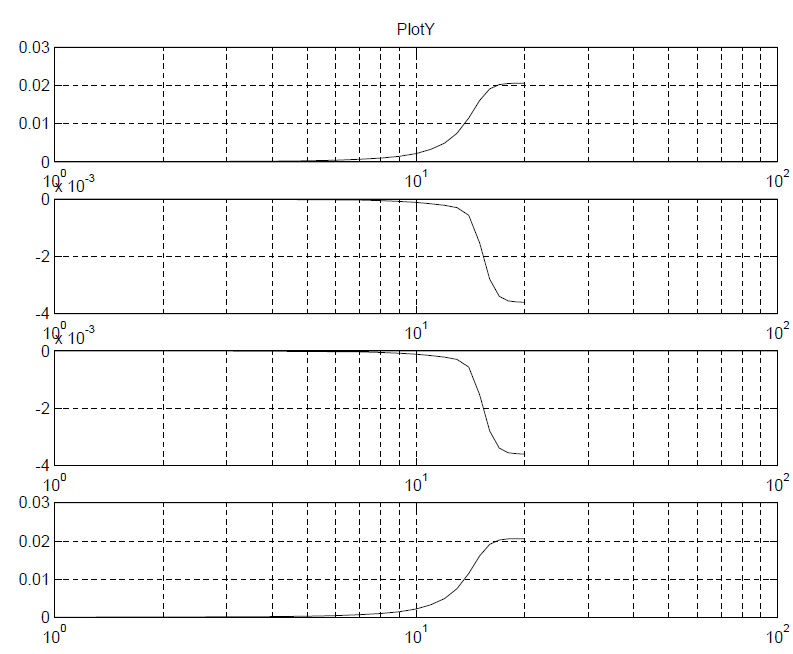

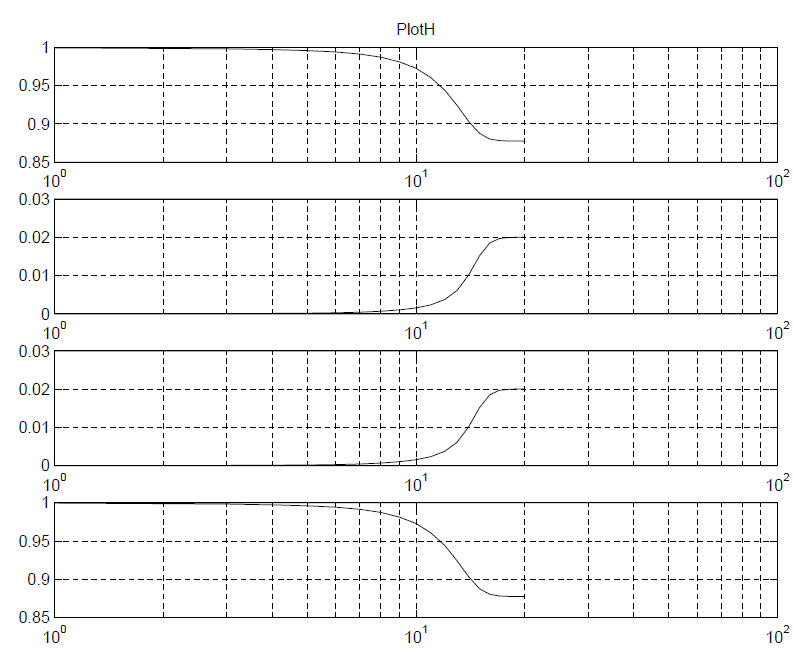

對於前三個步驟,我簡單地寫了兩個Matlab scripts 來模擬兩條藕合線的情形:

阻抗函數:

傳播函數:

輸出:

以matlab編程的話則上面的程式看起來簡單得多;實務上多數的仿真器(含SPISim的SSolver)為了仿真速度上的考量都是以原生碼(C/C++)編程而成,故在matlab裡簡單呼叫即可的矩陣操作如inverse, eigen value, LU decomposition等等都會因在原生碼語言中所用函式庫不同而多顯得冗長複雜許多。

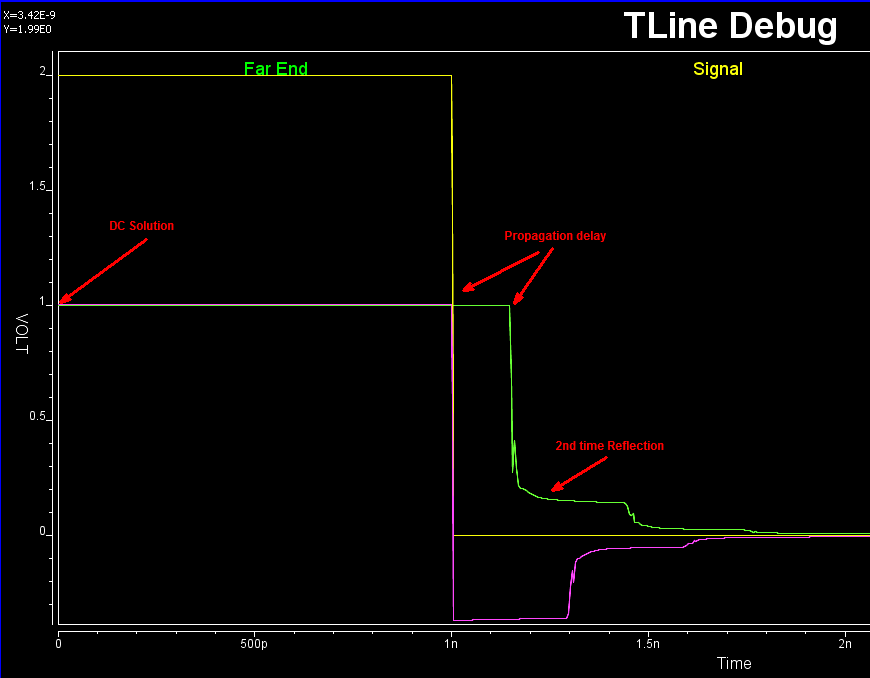

最後,很少剛為元件建模完成即可直接運作無誤的,很多情況後面除錯所花的時間精力會較前面開發的期間更多;對傳輸線而言,因其多為多條線藕合、且由極零方程轉到時域的方程又有很多項、再加上有些信號得等上傳播遲延後才會由另一端傳來,故在除錯上是極具挑戰性的。一般上我們是用divide and concour的方式先把問題簡化到最少再一項一項來修正:比如說先除錯單線,阻抗完全匹配(故無反射),且特性阻抗為已知(故可查入射的振幅)再從DC位準來的除錯等等,這樣便會顯得有頭緒許多:

SPISim SSolver傳輸線建模的根據論文和HSpice所本的是同一篇,有興趣的讀者可依下查閱:

“Optimal Transient Simulation of Transmission Lines” by Dmitri Borisovich Kuznetsov, Jose E. Schutt-Aine, IEEE Trans. on Circuit and Systems, I Feb. 1996

教科書方面個人則以為Dan Oh:“High-speed Signaling”, 也就是我們相關書籍選列中的第S6 於第五章部份解釋得較詳細;這也可能是因為原著者也在相近時期與上述論文第一作者自同一學校畢業之故;最後也值得一提的是上述傳輸線的建模方法也常可應用到其它不同的元件,比如說是同是均質被動、以S-參數表示的system channel。在將頻域資料利用vector fitting轉成有理化式的過程中,一些原有的S-參數問題(causality)即可透過這個程序來修正。