系統完整性分析大致上可分為幾個領域:信號完整性(Signal Integrity)、電源完整性(Power Integrity)及電磁相容性(EMC… Electro-Magnetic Compatibility)等等。分析的方式通常是先經由對被分析元件或通信渠道建構模型、而後透過軟體進行仿真。

在談更多的細節前,我們需先為所謂的”系統”做一定義:

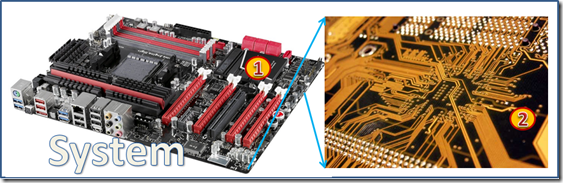

上圖(1)中所示為一常見的電腦主機板;在板子最上層的元件多包括了散熱器、各種的電容及末端的連接器等等。若把板子翻過來..如圖(2)所示,我們則可看到很多的焊接點及在電路板上的佈線(PCB trace),如此類的非晶片內部的、可宏觀上用肉眼看到的系統即是我們所定義系統分析的範疇。唯這類系統並不侷限於電腦主機板,舉凡手機電路板、內篏式系統或甚至是大型伺服器裡的電路亦可含括在內;以上所舉的這些例子宏觀上均可以用肉眼看到…差別只在於大小。之所以不將晶片上的設計包含在系統分析之內是因為其相對尺寸較小…對於一般傳訊的波長、信號失真的幅度遠比在我們所定義的系統上來得小。

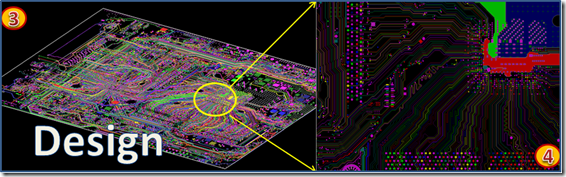

我們剛剛談到的這些系統多是用電腦輔助軟體所設計而成,若我們能把設計圖如圖(3)放大來看,可以看到許多的佈線從晶片邊緣的針腳(Pin out)走線透過導孔(Via)經過不同的PCB疊層而走到板子邊供輸出輸入的各類連接器,如圖(4)所示。

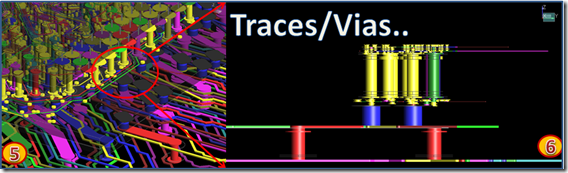

若我們能繼續放大以三維模式看這些針腳及導孔附近,如圖(5)所示,則可發現這些宏觀上毫不起眼的細微之處,實為各類圓柱體所建構相連接而成;圓柱體穿過疊層間(Layer stackup)而連到電路板上專位信號或電源預留的走線層(每一電路板在上下兩層間實為數層不同的電源、走線層與不導電界質(medium) 交互壓縮而成),在這一連串走線的兩端是晶片的封裝(package)及連接器(connector)。電氣信號從晶片裡的緩沖器而始、經過這一連串的走線及導孔、最終來到連接器。連接器之後亦經同樣的程序最終走到彼端晶片內的接收器。如果說這端的源頭是電腦處理器(CPU)或晶片組(chip-set)的緩沖器,彼端可能就像是如記憶體(DDR)或USB的各類裝置裡晶片的接收器。

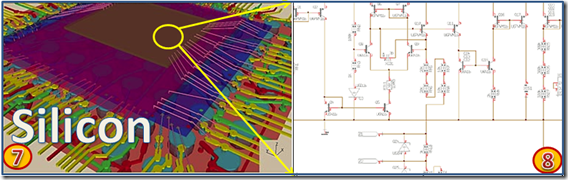

當我們把這些在傳送或接收晶片裡的緩沖器(buffer)調出其設計圖來看,則可看到不同大小的場效體(MOSFET)以相應的邏輯方式組成。不同位元(bit)的信號由其前級的電路輸出後,透過這些緩沖器對信號加以放大及加強以便能在不失真甚鉅的條件下透過剛才所述的走線、導孔、連接器或甚至是中間的藕合電容等達到另一端的緩沖器對已衰減了的信號加以復元重建。為減少衰減的情況、這些欲傳送的位元信號也可能先進行編碼,再在接收端進行解碼。

系統分析模型:

由上所述,我們可以看到若欲對我們剛剛所定義的系統做完整性的分析,則必需先對其中所牽涉到的各種元件及因素(整理表列於下)做些了解。如此才能為其建構模型而進行仿真分析:

- 輸出、輸入緩沖器: 通常是以IBIS或Verilog-A所描述;如何為其建模等等;

- 晶片的封裝:各種封裝的方式及其建模;

- 電路板及其疊層:不同疊層、介電質及通信、電源層設置的影響;

- 走線(傳輸線):如何為失真的因素、如串擾(Crosstalk)、等做分析;

- 導孔、連接器:如何設計、建模並分析其傳訊效能;

- 通信渠道:各種佈線、佈局(topology)方式及端口阻抗的設計;

- 信號:不同界面(PCIe, USB, DDR等)的不同信號方式及差分信號及其等化等等。

我們將試著在這個SPISim的版面, 為以上所列之建模及分析方式做一簡單的整理介紹。