備註:

對此貼文有興趣的讀者或可繼續在 [Part 2] 得到更多相關資訊,並至 [Free Web App] 使用此一模型轉換流程的免費工具。

IBIS to Spice:

系統完整性分析中,大部份的建模流程都專注於由原始設計(Transistor)透過Spice網表格式轉成為IBIS模型。但基於以下數點的考量,我們也常發現相反的建模流程、即從IBIS轉成相對應Spice的函式庫格式 (Subckt library)亦有其存在的價值:

- 支援開源或免費的仿真器: 網上有數款開源或免費的Spice仿真器, 如 Berkeley 3f5, eispice, ngspice, LTspice 等等。這些仿真器多將重點放在晶片上的BSIM模型或廠家所出產的元件, 如LTSpice的穩壓器(Voltage Regulator)等等;當用在系統分析上時,雖然它們對傳輸線大多也都有相當程度的支援,但對於輸出入用的緩沖器(常以IBIS模型資料形式出線)的支援則是付之闕如。在沒有原始設計的Transistor網表、又不能使用相對應的IBIS模型情況下,這些免費的仿真器就只能束之高閣了。當然若有足夠的經驗及能力,吾人也可編程而直接在這些開源軟體裡加入對IBIS等的直接支援, 但這過程是需要相當時日才能完成的。比起若能直接透過某種流程而能將現有IBIS資料轉成這些Spice也能直接使用的模型而言,後者的所需的工程便小得多。而且若這流程是建於Spice之外,則當工程師有需要快速地做些完整性仿真時,便可運用手上任何一款的相容仿真器而不用另外使用特別編譯的軟體。

- 讓模型供應商能提供公用的參考資料:IBIS本身雖是業界公用的格式,但其在仿真器內的實際體現則依不同廠家而有不同。在理想情況下,不同的仿真器對同一IBIS模型的運作應會生成近似的結果。為了達成這個目標,IBIS制定委員會也定出了”Golden Waveform”的資料格式以便模型使用者能對所用的仿真器的精確性能有所初步的檢定。實際上,這個”Golden Waveform”並非強制性地需在IBIS模型內提供而許多模型也都對此付之闕如;故而有些模型供應商 、如美光半導體,便轉而提供編碼過的Hspice原始設計網表以做為仿真的參考。如此一來,它的模型使用者便必需要有Hspice才能仿真編碼過的設計。我們認為若能在現有IBIS模型之外,更提供一未編碼Spice網表而且它可透過人人可免費得到的開源Spice來仿真進而得到與IBIS極近似的結果,反而更能體現IBIS在業界是公用格式的精神。

- 外顯地實現IBIS的運作原理及流程更具教育性及參考價值:網上隨便一找都可以發現很多談到IBIS內部運作原體的論文及簡報。這些內容或可以供大致了解模型運作的過程所需,但魔鬼多藏在細節理,模型實際上多以C/C++編程、實現且運作於仿真器內而非外人所知;我們認為, 若能將這些原理以外顯的方式實際以Spice的格式呈現出來,進而能透過仿真而產出和其它商用軟體極近似的結果,則更富教育意義且具參考價值。

- 開發流程的考量:仿真器是系統整合分析流程裡重要而不可或缺的一環 (場解器亦如是);做為一分析工具供應商,我們有以下數種選擇以便能在開發的流程裡有仿真器可做運用:1.與市面上已具規模的仿真器供應商合作而要求我們的客戶都必需要有一分License; 2.內部從無到有自行研發; 3.使用現有的開源且有聲望的仿真器。上述選項各有其優缺點且不互斥。對於一新創公司如我們而言,需要在有限的時間及資源內為客戶提供最高CP值的工具,則第三個選項、即使用開源版本並再加以改良、便成為最具吸引力的選擇。

市面上已有數家公司提供Ibis2Spice的流程。它們之中免費的版本多提供到IBIS Ver 2.1的轉換支援。即便是付費的版本也只支援到Ver 3.2。再者,它們所轉出的Spice模型多不能直接在開源Spice上所使用。我們開發的目標是要能支援到Ver 5.1的電流資訊、亦即[ISSO] 及 [Composite Current]等資料的運用以能做SSN的雜訊分析。在含此文第二部分的這兩篇貼文裡,我們將對本公司所開發的Ibis to Spice流程做一簡介。首先會談及的是如何運用IBIS裡的Ramp Rate來轉換出相對應的Spice模型,而後要談及的是更精確的、即運用Waveform data來建立模型。兩者我們都會佐以和其它商用仿真器對同一IBIS模型仿真的結果來證明此流程的可行及結果的精確性。

流程開發的目標:

- 轉出的模型能直接在開源仿真器、 如Spice3f5 及NgSpice上運作

- 支援電壓部份的Waveform data (Ver 3.2 andup)及電流部份的Composite current (Ver 5.1 and up)

- 能與其它的業界所常用仿真器產生極近似的結果。

由IBIS裡的RAMP資訊做IBIS to Spice的模型轉出:

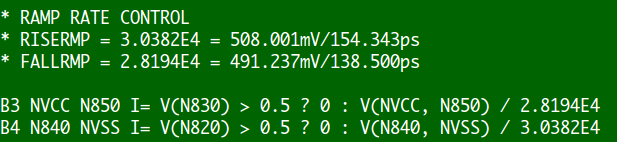

首先我們來看一下現有以RAMP為主的Spice模型轉換,因市面上其它工具所轉出的模型不能在免費Spice上直接使用,在我們的免費工具SPILite裡,我們也已加入類似的功能以便能直接使用NgSpice。這部份的流程主要是將原IBIS模型裡的RAMP資料取出並用於瞬態仿真時。靜態電流部份、即PowerClamp, GroundClamp, PullUp及PullDown的資料則是用免費Spice裡支援的ASRC有源元件來實現。這部份在下一貼裡所將提及的:用IBIS裡的Waveform來轉出Spice模型裡,將做更多的應用。

在網上搜尋Ibis to spice則會找出一篇貼文:IBIS to Spice Translation (part 1), 在此文中,原作者討論了市面上其它工具做Spice模型轉出的工作原理、及他所試圖改進的設計及結果。他也提供了一Awk程序以便能將原始Spice模型在當時的免費Spice裡使用。由於這篇貼文是十多年前所寫,當時很多的觀察在今日均已不再適用。比如說:現今公版的NgSpice已可直接讀入如X+-3.2的語法而毋需再將其轉成X-3.2, 故其Awk程序似已無用武之地。無疑的,由於文中所提之商用工具最後更新似是在1998年,原理圖至今仍未做更動,故就研究其運作原理而言,原貼文還是有其參考價值。

上述貼文的第二部份是如何將利用Ramp資料來運作的原理圖。在網上要找到原文恐怕比第一部份難得多,我便將其重貼於下以省讀者的時間:

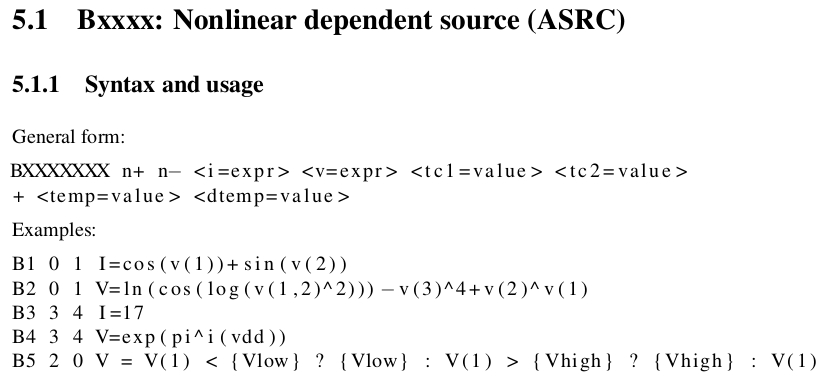

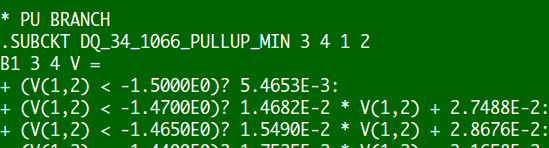

原理圖中的主要原件是四個靜態電流元件,即XPWRCLAMP, XGNDCLAMP, XPULLUP 與 XPULLDOWN, 它們是利用Spice裡的ASRC(Arbitrary SouRCe, 即任意源元件)來實現。在Spice的使用手冊裡,我們可看到其語法及功能:

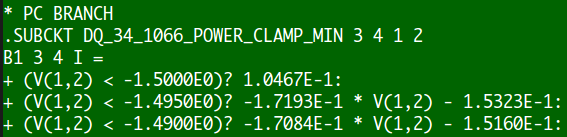

由於Power Clamp(PC)及Ground Clamp(GC)是屬於ESD電路的一部份而始終是有在作用的,故其資料可直接被使用。在實作上是將IBIS裡的IV對應表先轉成每兩點間的線性直線(Piecewise Linear)方程而後輸出電流。以PC為例, 由下圖中可看出端點1,2間的電壓被拿來做查表內插而將算出的電流由端點3,4間來供應。

對於Pull up (PU)及Pull down (PD)分支而言,由於它們是在輸入信號切切換後才漸漸開或關的,故在以原理圖中是以在左上部份的C1及RB3所供應的RC充放電常數來完成此開或關的目的。在瞬態仿真中,此RC參數先被RAMP的值設定於分母的部份, 而後將乘上由PU等所提供的原始值,最後再以G控制源元件(VCCS,電壓控制電流源)來將電流輸出。

在原貼文裡,原作者也提及他曾試著直接以其它方式來取代以此RC來做PU/PD電流切換的方式但效果不彰。我們認為其中可能的原因是因為PU/PD供應電流值是有瞬態時間因素的,即它們不是馬上就如PC或GC般全開或全關的,故若少了這“漸漸打開/關閉”的運作,則輸出電壓會很不平滑而可能造成仿真不收歛。而且就算收歛,結果也不會準確。也就是說,一般輸出緩沖器裡場效體(MOSFET)通道裡的載子有其一定的速度,故其開或關的時序不會在瞬間完成。

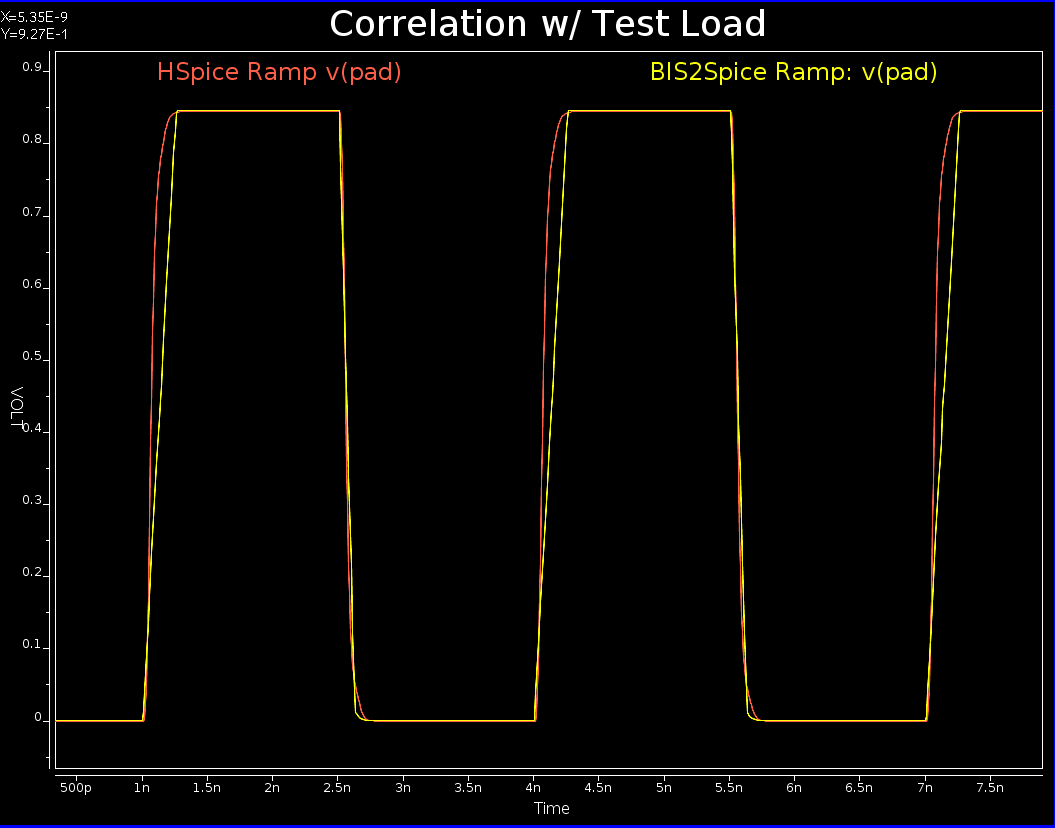

透過這種由RC方式的開關模擬,來仿真由IBIS轉出的Spice模型,再與其它商用仿真器對同一IBIS模型在相同負載情況下仿真結果相比較,我們可看出其結果算是相當接近的。但這相近僅止於PAD或PIN點的電壓部份。當測量其對供應電壓源所使用的電流,則可發現兩者相去甚遠。也就是說:這種Spice模型只能做理想供壓情況下的信號完整性分析而不能拿來將SSN列入考量。其次,上升/下降的曲線會呈現出如RC充放電般的曲線而非直線性。對於仿真速度而言,因為這種實作的設計相對簡單,故可很快地完成仿真。。與直接使用IBIS的商用仿真器相較之下並不會慢太多。最後要再說明的是:不像IBIS模型裡各種Typ/Min/Max的資料都在同一表格內;當要將某一IBIS裡的模型轉出做Spice仿真時,欲使用之不同的Typ/Min/Max Corner均需分別地各自先被做轉換。

這篇貼文係為於DesignCon 2016同時舉行之Ibis Summit所準備;我們在這會中宣讀並展示此研究結果。讀者請繼續參閱「之二」之貼文並可在那下載相關文檔及範例。