流程構思:

我們設計差分放大器的建模流程時,考慮的是與單端點放大器建模流程的一致性及為因應兩者間不同處所加入的彈性。以前者而言,差分及單端放大器所需走的步驟有很多是相同的︔這是因為差分模型中有一大部份所獨立出來的便是單端放大器(請見上一則貼文)、故自需為其依單端模式建模。對彈性而言,主要的考慮是差分建模過程中,對於靜態和靜態差分電流的建模容或有以人為做取捨的空間。在這篇文章裡,我們就再就中間的細節做更多的探討,並看看在我們的SPIBPro裡是如何兼顧這一致及彈性的。

模型設定:

理論而言,建模者並不需要先對所建放大器為可以單端點方式建模的假性差分(pseudo differential)或半/全(half/true differential)差分來做分別;在官網上的IBIS Cookbook也是如此地陳述。其甚至以一加碼後的spice設計為例來說明在無法得知所為建模的設計內容的情況下,可視一黑盒子而直接以差分建模方式將其做半/全差分設計來處理。直至以series model來表示的差分電流算出來後,再依其是否達到足夠影響另一輸端的大小(亦即藕合的程度)再來決定半/全差分的假設是否正確。

實務上來說,我們認為應反其道而行:也就是先以假性建模方式進行,若模型驗證的結果顯示精確性不夠才再來考慮走半/全差分的流程。之所以如此建議,是因為一般同公司或由公司外包的人才會為其設計建模︔故是否有藕合的情況通常只要問一下晶片設計者就知道了、且如此做也不需要知道晶片設計或運作的內容或細節︔再者,差分放大器的建模需要一些額外的掃描、仿真及計算,故除非絕對必要、能免則免。

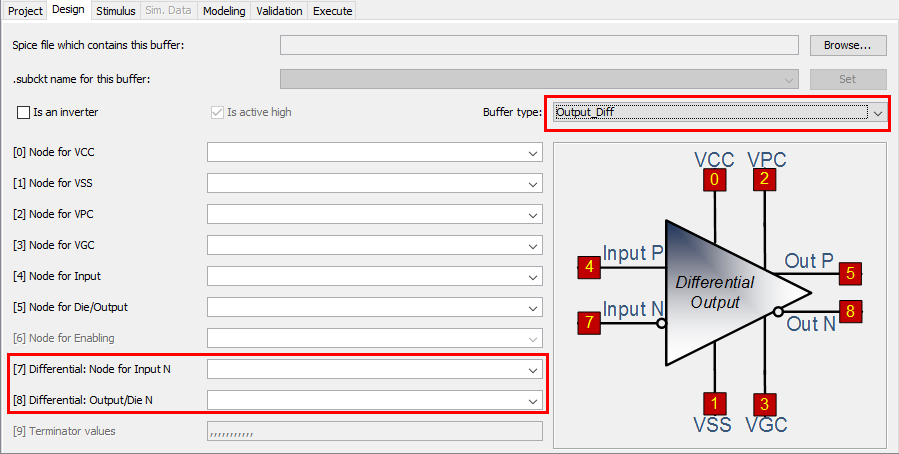

相較於為單端放大器建模,為差分建模所需要的設定,多需要知道的只是額外的反相輸入及輸出端點連結在原transistor電路所需連結的端點為何︔再加上差分模型的指定,便足於開始建模的進行:

流程概觀:

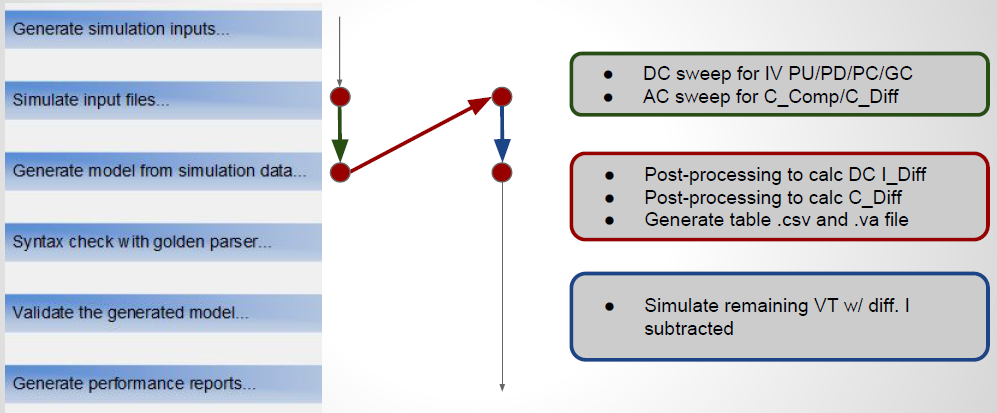

差分建模的流程大致總結如下圖所示:和單端放大器建模主要不同點在於走向非線性而可一氣呵成。包括仿真及後處理的步驟都需要前後進行兩次:第一次仿真只需要針對為IV做掃描的PU/PC及C_Die進行即可;注意的是因為兩個輸入互為反相,故並沒有需要做PD/GC的仿真,它們的資料在PU/PC仿真結果裡都有了;第一次後處理的階段需要進行的是將同模電流自PC/GC結果裡萃取出來並分別存成PU/PD/PC/GC各曲線的資料以供第二次後處理所用;而減去此同模電流後的差分靜態電流部份便需以csv表格的格式外存以供用戶用其它如試算表等的工具做檢驗或另作建模所需;其次,C_Comp 及C_Diff的值也需自C-Die的仿真中算出來;與已經算出的靜態差分電流,這兩者需在後處理結束之前以可仿真的模型來呈現。第二次仿真階段只是利用這才產生的模型,將其瞬態電流在VT仿真中自原差分設計後除去;也就是說第二輪的仿真過程只需用到VT的檔案︔在此之後,所有的資料都已具備,故在含第二次後處理的階段之內的建模流程就可繼續線性地走下去、就好比是為單端緩衝器建模一般。

IV資料建模:

雖然PU/PC的仿真是為在DC模式所需的電流所做,但由於很多原始設計裡都有時脈信號的關係,這些仿真並無法真的在DC模式下來進行︔所以走的方式多是"假DC"(pseudo-DC)、也就是所有的時變信號都變動得很慢而使得在每一個取樣點附近都可看做是已達準態的情況;如此做的另一考量是很多的設計由於其複雜性,都得透過如all sources ramp up的程序來得到靜態DC的初值,故若真為每點都如此做則仿真所需的時間便會很長。

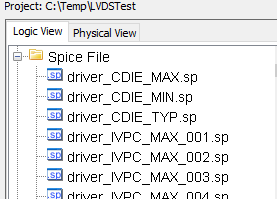

另一個能縮短仿真所需時間的方式是平行處理:如上方我們SPIBPro所產生的test bench電路所示,不同IVPC的檔案間不同的只是輸出N點的電固定電壓,輸出P點則同是做線性-Vcc~2Vcc的掃描︔正因為兩者之間無關聯性,故所有這些spice檔案都可以並行地在同電腦上用多執行緒或是在不同電腦上被仿真;另一流程上所需的考量是因為並非在所有的偏壓點原始設計的仿真都會收歛,故在後處理上需對部份資料的缺少有相當的容忍性。

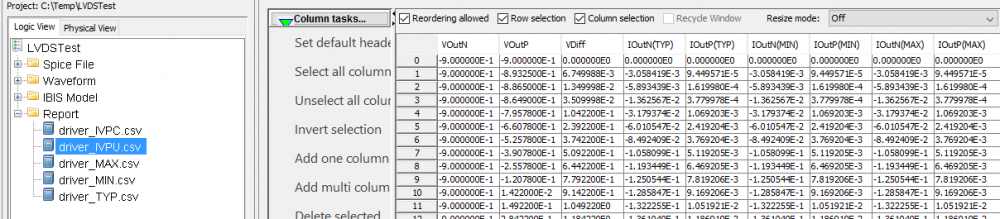

如前所述,第一次後處理時需做第一個部份是的是將才剛完成的IV仿真做計算,先把同模電流算出來,其次將這同模部份在每一點都減去以剩餘差模的部份、最後再將這些不同仿真的結果總結並輸出在一個CSV檔案裡。當然以這些資料做初始的建模【下段會詳述】是程式需要做的部份,但同時也提供CSV檔也表示如果有需要的話,用戶可以認證這些資料或以其它的程式(如試算表或JMP)等來自行做建模的實驗。

那要如何將此表建出可在第二輪VT仿真裡可用到的模型呢?有下列兩個可能的方式:

- 曲面反應模型:

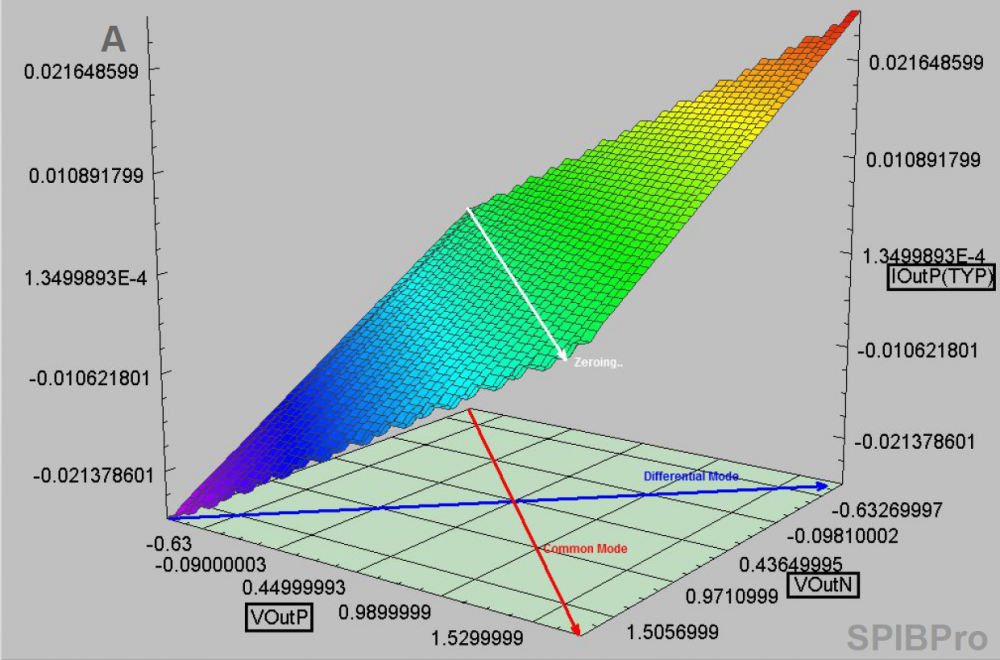

在此要做的是將上表的資料以三維的方式呈現,如上圖所示,因為差分放大器P/N兩端的輸出一般是有對稱性的,故吾人可在與同模(紅色直線)相垂直的準差模部份(藍色直線)來看在那軸線上的資料是否可用線性的平面來表示;若然則表示只要用一個電阻放在產出的藕合部份的模型裡即可︔若是以series model 來看便表示只要一個series resistor即可。在驗證上,同戶也可利用產生出來的CSV檔來看P端輸出電流和差分電壓(即V(P) – V(N))是如何變化︔若是其值大部份近似固定值、則此固定值便是模型裡所需的電阻值。

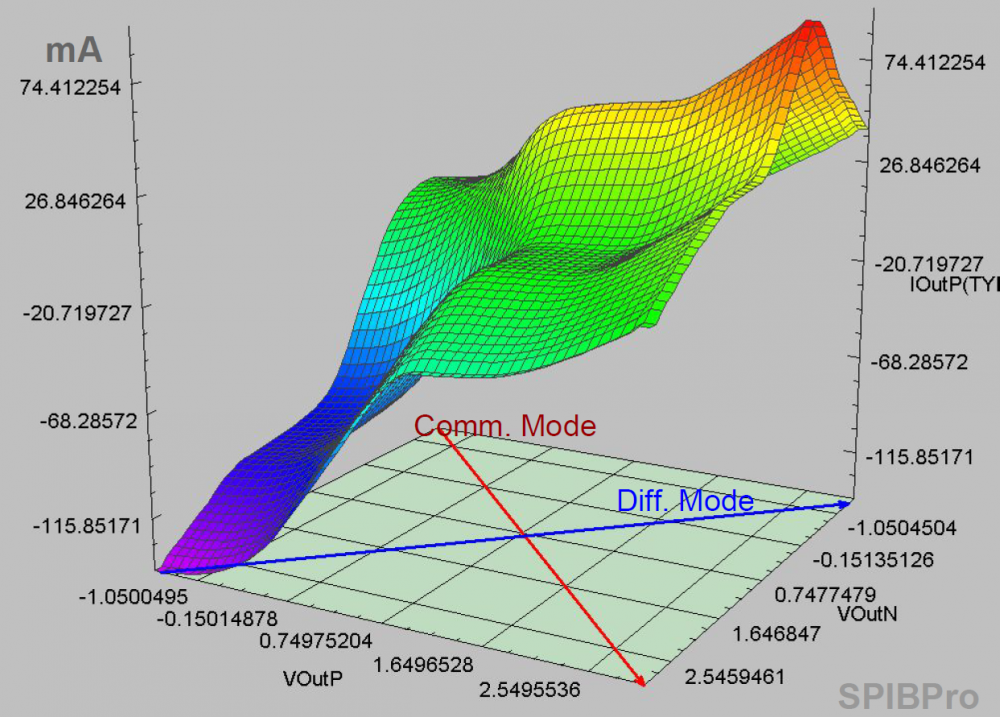

其次,若是軸線上的曲面並非直線,但是是一致的波浪狀,則表示用一非線性電阻仍可以表示這波浪面︔在為VT仿真電路所需的實現上則可用如PWL的被控元件以達到非線性電阻的目的。至此而言,可以說的是一個差分建模流程裡應要有輸出CSV及3D視覺化資料的能力以變對所需要的模型設定很快地有初步的決定。

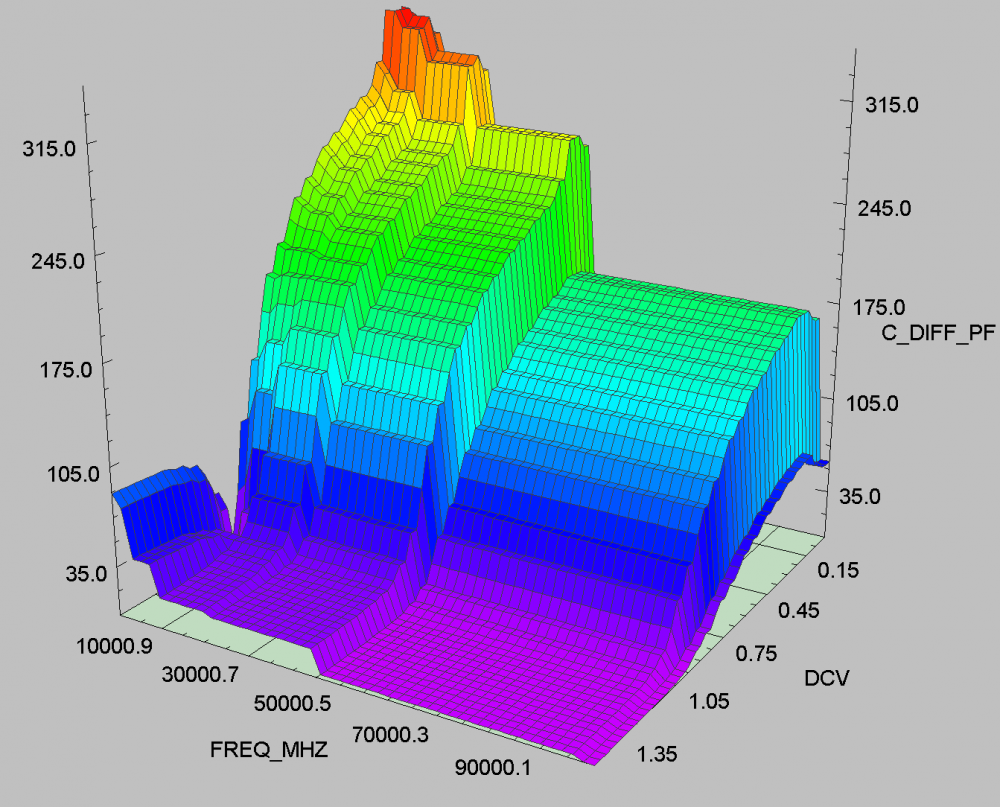

比較麻煩的是若資料呈現出的是如上圖般的不規則曲面,則需再透過如為"反應曲面"來計算或是以Series MOSFET般用多重表格來給與所有取樣點才能得到精確的建模以供VT仿真使用。

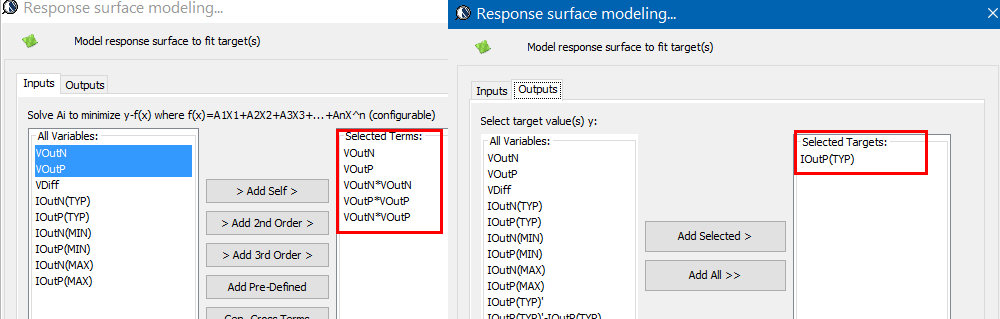

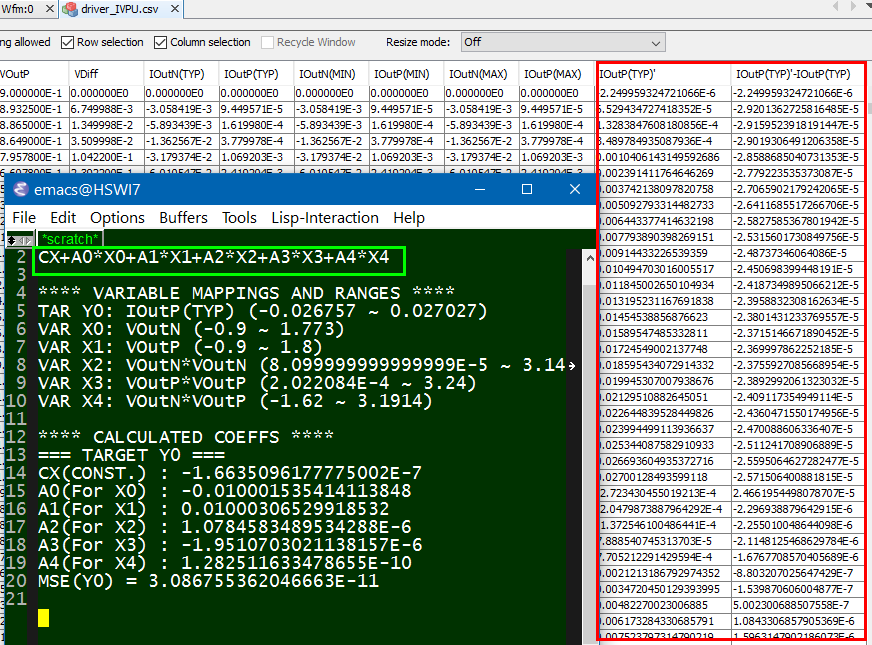

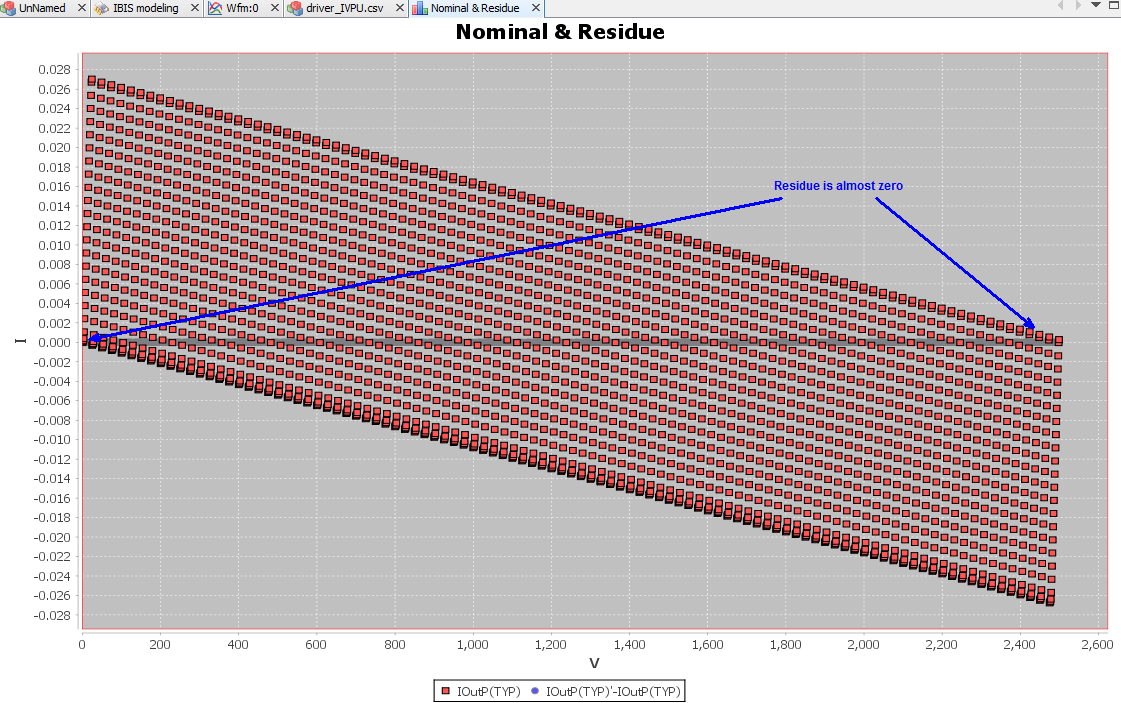

以反應曲面設計為例,上圖所示是我們SPIMPro的步驟:選定自變數及應變數後時也需決定自變數的order為何︔一般而言二階應是足夠,而後就用每一取樣點形成的矩陣做SVD解並求得各個階次自變數的係數為何︔同時也把原取樣點的各值代入此等式中再和原輸出值求差值、亦即計算殘餘值(residue):

若是求解成功,依此預算式算出並和真值差的殘值應是很小,若能以視覺化來檢查(如下)則能很快看出所求等式係數的品質:

上圖各紅點是真值,而很靠近原點的灰色部份則是殘值;因殘值極小,故可謂求解成功;接下來要做的便是利用spice 元件裡的E/F/G/H等受控電路再依仿真器所支援的等式格式(如用poly(2)來表示二次式並在其後設定各係數值)來產生模型︔以上的圖形皆由我們SPIMPro所產生︔若所用工具無此功能,則可利用Matlab以"lsfit"的函式來進行。

- Series Model:

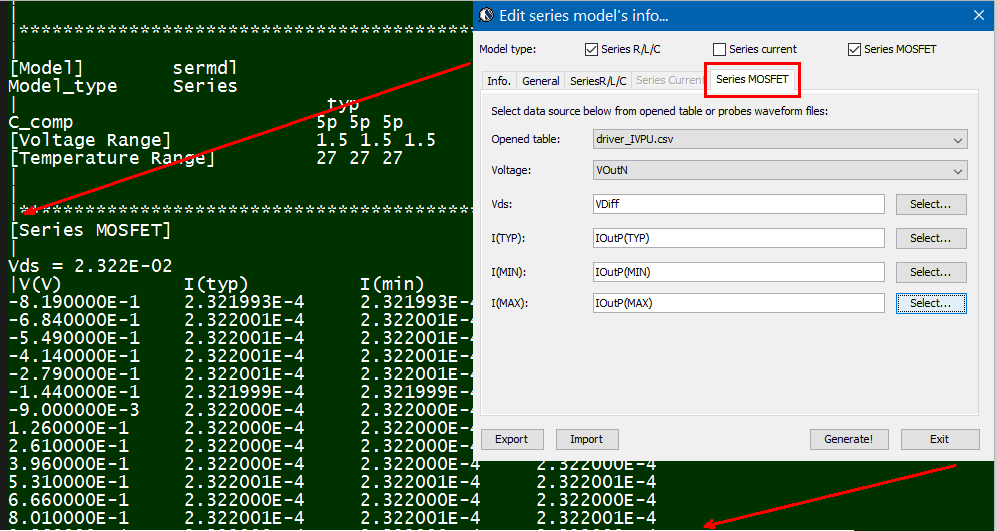

若是建模者想直接利用CSV表格建模供VT仿真使用而不想走上述幾個為二維曲面建模的步驟︔在所用仿真器也支援series model的前提下是可以直接進行的︔所要做的便是以合乎IBIS語法的方式來將CSV表單直接轉成series model,如下圖SPIBPro的 series modeling flow所示:

若建模者可事先利用3D視覺化了的資料預先決定只要用簡單R或甚至非線性電阻以series current的方式填入series model,則過程並不複雜;但若是要用可達一百個表格的Series MOSFET來把所有取樣點都加進去,則要手動來做所費的工夫就很不經濟而不如透過如我們的程式來進行也更不易出錯。

C-Diff建模:

與上述類似的步驟(CSV建表及曲面建模)也同樣可套用在差分電容C-Diff的計算上︔話雖如此,由於利用EFGH等受控電源及透過series model的語法對電容的描述有更多的限制(比如說用以描述非線性電阻的series current及series MOSFET就無法套用到需取決於時下端點電壓變化率的電容值CdV/dt),故一般的做法、也是有所取捨的部份,是在所得反應表面的最高及最低值間取一平均值,而後再加入所生成的模型並在VT瞬態仿真上使用。

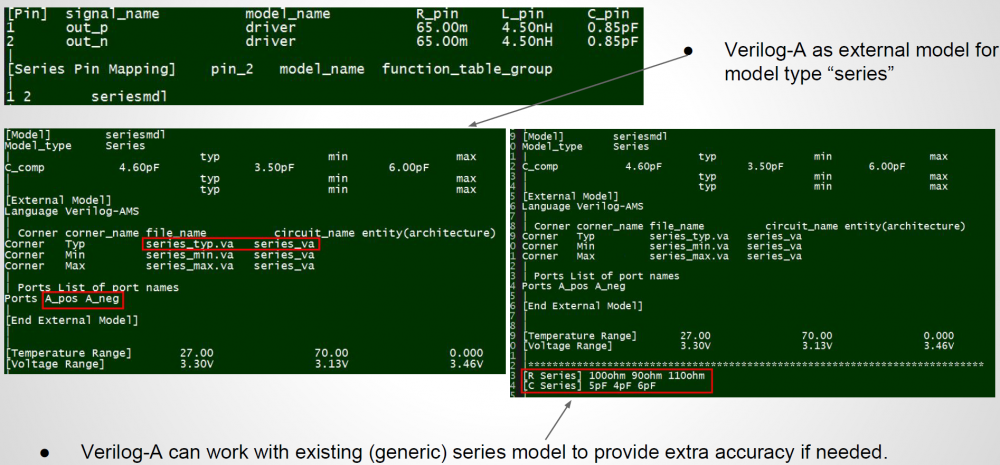

Verilog-A建模:

在我們為年底IBIS Summit所遞交的論文裡,另外提出了以Verilog-A/VHDL等為series model建模的可能;其優點在於當用於流程上時,可利用其語言內建的$table_model函式直接運用第一次後處理所產生的CSV表檔︔其次,由於其亦含有更多的運算子(如可以用ddt運學子來算出端點電壓變化速率),故在對C-Diff值的建模上可有更多的彈性及更高的精確度。相關細節待會議發表後再於此更新。

模型完成:

在前一篇的貼文裡,我們已經略述如何利用series element加在P/N兩端的差分腳位上來加進藕合的影響︔另一種可能是純用Verilog/VHDL等語言直接用differential model類別加在腳位所連model下的敍述︔當運用我們所構思的、只運用到series model的Verilog/VHDL模型時,上述兩者其實是可以一同使用的。如下所示:

上圖中,在”[Series Pin Mapping]”下仍描述有另一series model跨接在P/N腳位間並提供藕合的資訊︔然而另一針對此series model所建構的Verilog/VHDL模型透過以series 為model_type的方式用”[External Model]”來加掛於頂層的series model之下。與純series element描述式不同的是因為可用到許多Verilog/VHDL的運算子,靜態差模電流可更方便地被表示︔而C-Diff也可以更精確的模型建構出來。和純differential model 為model_type的作法不同的是,這些Verilog/VHDL的語法只限於描述series model的部份、而且其是可以被comment out掉以增進模型的可攜性的。也就是說,我們可以得用更高階次才能描述的部份放在這裡,而在上層的原來series element裡放入基本的差模IV及單值C-Diff,便可同時達到可攜性及彈性增進精確度的要求。

流程驗證:

欲驗證一差分建模流程的精確性,當然最終的方式是將所建模型仿真的結果和原始設計相比較。但一開始驗證時,其實吾人可以用兩個相同的IBIS單端放大器模型,透過相反相的輸入再加上一任意建構出的藕合電路(比如說內含平行的R與C)、將其連接在兩輸出端來做為測試電路。由於這單端模型已以IBIS模式呈現,且藕合電路的內容也是已知,我們便可很容易地來和所開發的建模流程所產生的結果來相比較。第一次仿真及後處理後,所產生的同模電流放到PU/PD/PC/GC IV對照表裡且其值需是和原單端IBIS的同表格完全相同的;否則在同模的計算上便有錯誤。差模靜態部份應能完全反推出藕合電路裡的電阻值。。。不論其為線性或得用曲面表示與否;否則便是差模的計算有部份有誤;而C-Die的二維掃描也必需能完全反應出所設定藕合電路裡電容反應的部份。最後當靜態的差分電流及由C-Diff所形成的瞬態差分電流都能完全精確地在VT仿真中被減去的情況下,新建差分模形的VT表格便應和原始單端放大器IBIS模型裡的VT資料幾乎完全相同。

相關資料:

我們已於2016年十一月於IBIS峰會發表此一論文; 其可於 IBIS 官網 或 [這裡]下載. 我們亦於東京場次有現場錄音可[下載]