在前則貼文中,我們提到電路仿真器的核心部份是有由線性代數方法, 來對由節點電流及網目電壓方程所形成的矩陣做求解;我們也提到靜態及瞬態的運算中,元件部份被呼叫最多次的函式是”Solve”及”Stamp”兩式,也就是元件先依在那一時步的那牛頓迴圈中的端點電壓電流情況針對元件本身的物理方程求解,而後再將解出值填入矩陣式中的步驟。由於在熱迴圈(hot loop)內而被呼叫次數眾多,元件裡的這兩個函式便需務求精簡迅速必要以使仿真器整體運作能穩定、易維護且具延展性。

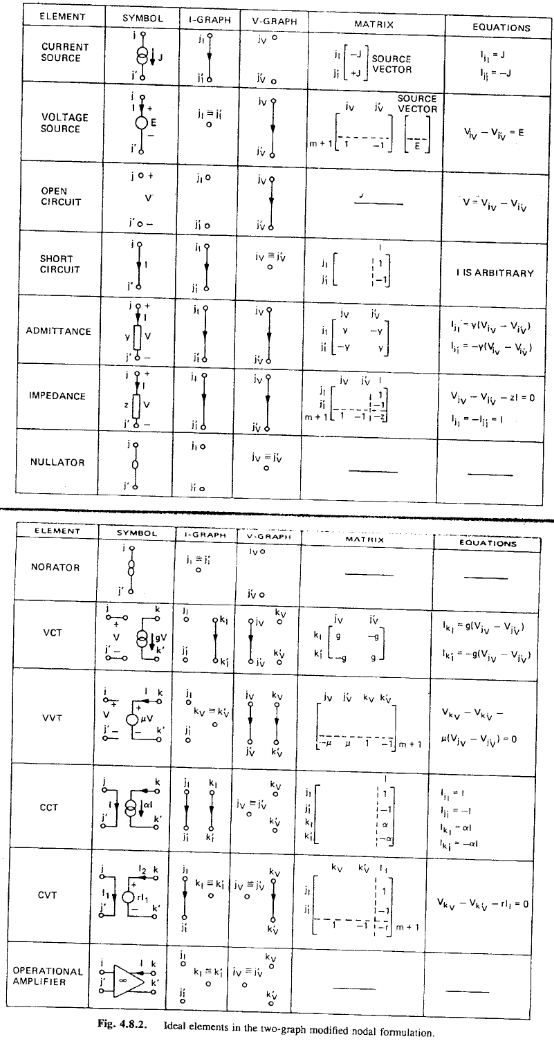

在前文底所列的經典電路分析教科書中 “Computer Methods for Circuit Analysis and Design” :第170頁列有元件值是如何被填入矩陣裡的:

從上表可見,在第一層的界面定義中(也就是元件的Solve函式裡)最主要的工作是不論單獨元件物理特性為何,均能由當下端點偏壓或所流經電流值而轉應成相對應的基本元件(如電流I、電壓V、電應G及電抗A)形式再依上表填入系統矩陣中。除此之外,由於牛頓法裡也要求要能提供一階導數以便在下一迴圈裡能更新自變數,故元件也要有能依端點情況提供一階導數(i.e. partial derivative)的能力;否則,仿真器將被迫以數值方式來對系統矩陣求導數,也就是在某一點情況下固定一自變數但依續變動其它自變數的方式來求數值上的導數(dV/dI 或 dI/dV),如此以來,將導致仿真速度明顯變慢且更不穩定(易不收歛)。

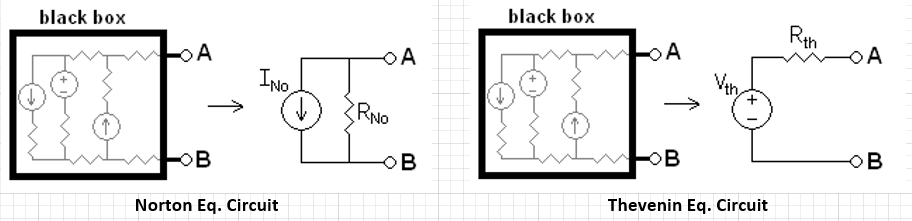

在理論上,不論一元件(即便如場效體或傳輸線等複雜元件)是否為非線性,其都可以藉由固定維持大多數自變數為常數的方式而得其線性化模型;比如說在某一時步(故t在此為常數不變)的某一牛頓迴圈(故端點情況為固定不變)的情況下,便可利用諾頓(Norton circuit)或戴維寧電路(Thevenin circuit)來達到簡化模型的目的:

上圖中,簡化後的模型已可用上述的基本元件(I, V, G, A)來表示而可依表填值;在我認為:這簡化的過程就是元件物理和仿真器相交集之處。

舉例來說,簡單的元件如R, V, I等等,程式只要依表填入到系統矩陣相對應之處即可;被控元件如E, F, G, H等也可被視為受控電阻或電感來依樣填值。較複雜的元件如之前提及的場效體、傳輸線或S-參數等當然就要事先導出數學式來表示其物理意義。專piecewise-linear電路或元件而應用的Katzenelson algorithm或可在此派上用場,即便是諸如電容或電感等的元件也得規畫一番才能填值;這兩者一般是用數值積分/微分器及Predictor來達成此一目的的:

從上述式裡可見:電容及電感沒有直接的電應或電感值可用, 而是得利用如數值微分的方式來進行;比如說簡單的Backward Eular dV/dt = (V0-V1)/(t0-t1)就可使電容C的電流變成有諾頓電路般I=Y*V+J的形式,而這J的部份則是由此電容過去的歷史值演算來而來。在固定時步的仿真器裡,這種簿計(book keeping)尚稱容易,但對非固定時步的仿真器而言dt的取捨則影響了仿真的精確度。而某些元件如傳輸線等,其線長也決定了信號傳輸的遲延故而也就限制了dt的值,否則若時步差過大,則由另一端入射或反射而傳來的信號變會被跳過了。綜上所述,可見一仿真器的研發真的必需由許多面向來考慮。

下面所示的截圖即為仿真器裡電容元件在熱迴圈裡的函式,讀者可由黃色文字的加註看到前述不同的處理:

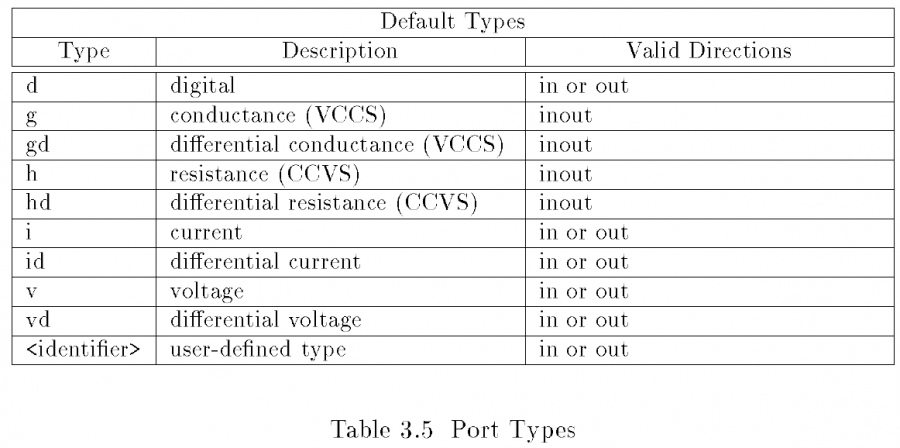

仿真器設計裡第二層的界面設計是有關於延伸性的考量。在前則貼文裡可見:以英文字首為始的二十六個元件大多已被使用,比如說R,L,C,I,G,E,F,G,H等字首都已約定俗成地表示電阻乃至於各類的受控元件;但除此之外若吾人要為特殊元件如天線、濾波器、特殊集成電路或甚至是將來尚未開發的元件來建模呢?一般而言仿真器都會有外掛的架構並以動態函式庫(dynamic link library .dll or shared object .so)用預定界面API的方式來達成此目的。拿Berkeley spice的仿真器來看,其定義的API如下:

可以看到能使用的類別較本文之初的表列更少了,更有甚者,藉由定義這些埠(port)及取用函式,仿真器可進一步限制了延伸元件對系統矩陣的存取而維護其穩定性。於是,設計元件以便能外掛於現有仿真器的工程師就得更進一步地把原有不論複雜與否的元件物理簡化成上述簡單API形式的工作了。

當這些簡化物理模型的方式導出之後,剩下的就仿真器研發部份便是逐一地把各個元件的模型利用數值及程設技巧先在DC或TR開始之初加以建模,而後在每一時步的每一牛頓迴圈裡依端點值計算更新模形參數而(透過API)提供給系統,再在每時步末為下一時步的所能取的dt加以設限且更新歷史記綠等等。

在我們SPISim使必信的SSolver仿真器裡,我們所參考的正是Berkeley Spice的架構且深為其設計理念及樣式所影響;在其原始版本及許多演化至今的其它開源版本裡,都沒有系統整合性仿真所必需支援的元件如: IBIS, 有損藕合傳輸線, S-參數及可定義如PRBS等的有源電壓等等;即便是S-參數的轉出,其它版本多也只支援雙埠電路(two port network)。由於過去的業界相關經驗,我們能夠相對輕易地了解其原本架構、流程而在較短的時間內加上這些元件的支持而達到應用的目的,但在閱讀相關文件及研發過程中,對這款在數十年前便已開發完成的仿真器,我們仍不禁且不時地為其設計之週到及流程之順感到敬佩,也建議有興趣的讀者能以其為本來深入地研究。